El procés de disseny del maquinari digital s’ha transformat intensament en els darrers anys. Per tant, es poden implementar petits circuits digitals mitjançant PALs i PLA. S'utilitza cada dispositiu per implementar diversos circuits que no necessiten més que el nombre d’i / ps, o / ps i termes del producte que s’ofereixen al xip específic. Aquests xips són inadequats a mides força modestes, normalment admeten un nombre mutu d’entrades i sortides de no més de 32. Per al disseny d’aquests circuits que necessiten més entrades i sortides, es poden emprar nombrosos PLA / PAL o bé un tipus més elegant. de xip es pot utilitzar anomenat CPLD (dispositiu lògic programable complex). Un xip CPLD inclou diversos blocs de circuits en un sol xip amb recursos de cablejat interior per connectar els blocs de circuits. Cada bloc de circuits és comparable a un PLA o un PAL.

Què és un dispositiu lògic programable complex?

L’acrònim del CPLD és “Dispositius lògics programables complexos”, és un tipus de circuit integrat que els dissenyadors d'aplicacions dissenyen per implementar maquinari digital com els telèfons mòbils. Aquests poden gestionar dissenys més elevats que els SPLD (dispositius lògics programables simples), però ofereixen menys lògica que els FPGA ( matrius de portes programables de camp Els CPL inclouen nombrosos blocs lògics, cadascun dels blocs inclou 8-16 macrocèl·lules. Com que cada bloc lògic executa una funció específica, totes les macrocèl·lules d’un bloc lògic estan completament connectades. Depenent de l’ús, aquests blocs poden estar connectats o no entre ells.

Dispositiu lògic programable complex

La majoria de CPLD (dispositius lògics programables complexos) tenen macrocèl·lules amb una suma de funció lògica i una opcional FF (xanclet) . Depenent del xip, la funció lògica combinatòria admet de 4 a 16 termes de producte amb ventilador inclòs. Els CPLD també difereixen en termes de registres de desplaçament i portes lògiques. Per aquest motiu, es poden utilitzar CPLD amb un gran nombre de portes lògiques en lloc de FPGA. Una altra especificació CPLD significa el nombre de termes de producte que pot aconseguir una macrocèl·lula. Els termes del producte són el producte de senyals digitals que executen una funció lògica específica.

Els CPLD estan disponibles en diversos formularis de paquets IC i famílies lògiques. Els CPLD també difereixen en termes de tensió d’alimentació, corrent de funcionament, corrent d’espera i dissipació de potència. A més, es poden obtenir amb diverses quantitats de memòria i diversos tipus de suport de memòria. Normalment, la memòria s’expressa en bits / megabits. El suport de memòria consisteix en ROM, RAM i RAM de dos ports. També inclou memòria CAM (memòria adreçable al contingut), així com memòria FIFO (primera entrada, primera sortida) i memòria LIFO (última entrada, última sortida).

Arquitectura de dispositius lògics programables complexos

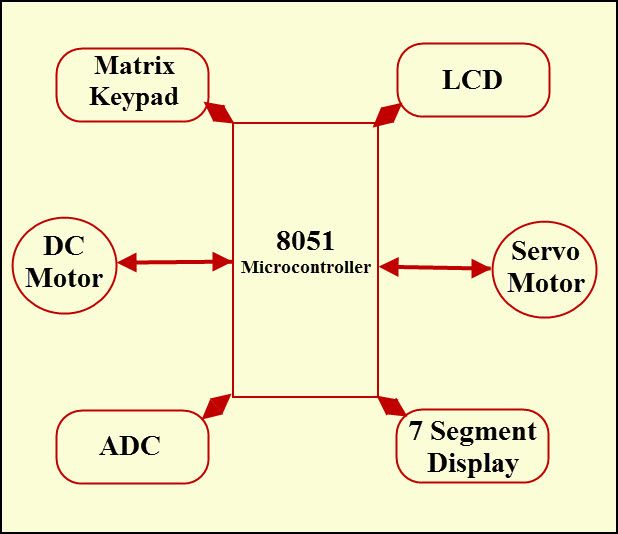

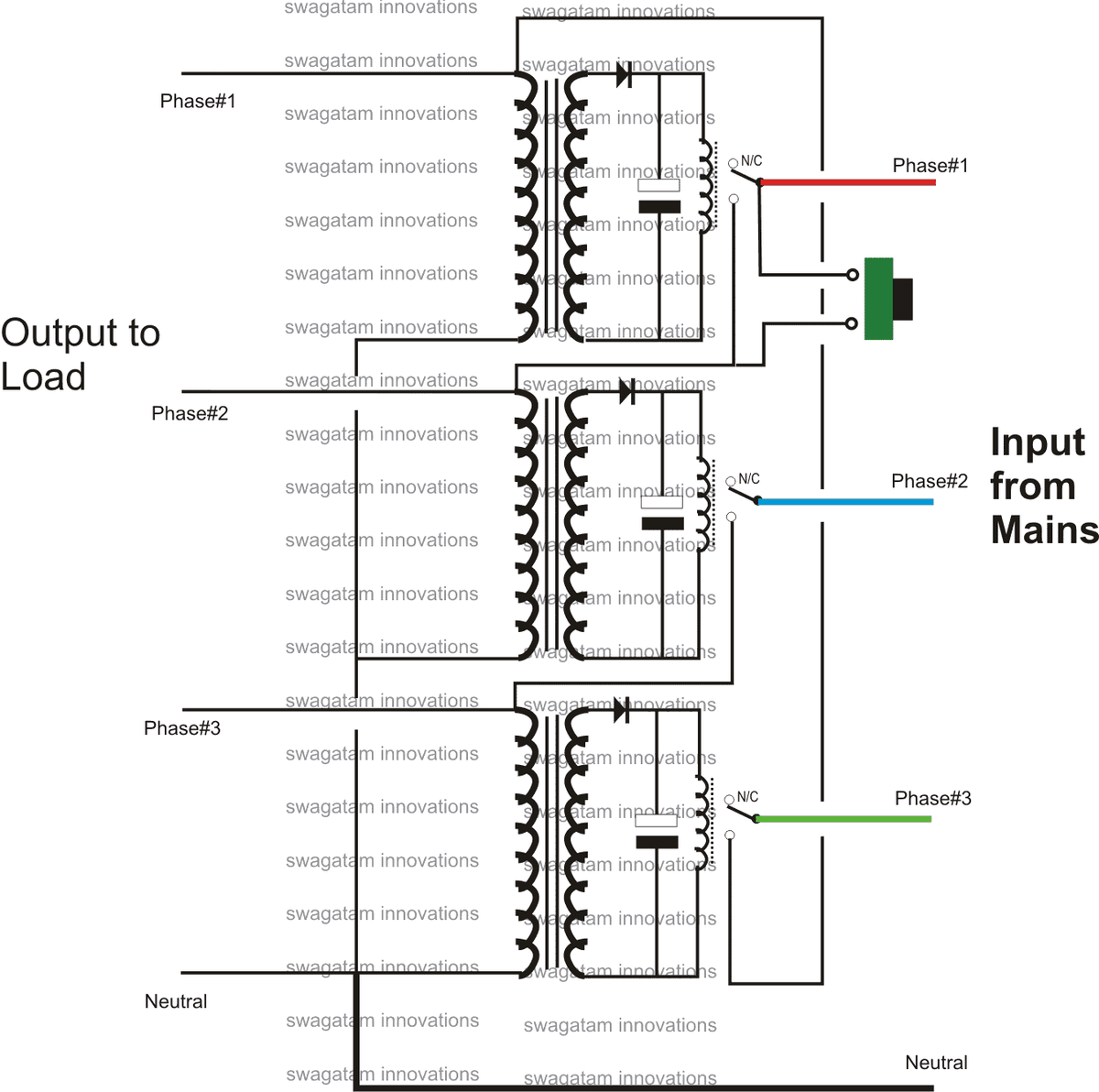

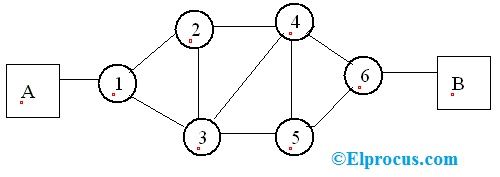

Un complex dispositiu lògic programable comprèn un grup de FB programables (blocs funcionals). Les entrades i sortides d’aquests blocs funcionals estan connectades entre elles mitjançant una GIM (matriu d’interconnexió global). Aquesta matriu d'interconnexió és reconfigurable, de manera que podem modificar els contactes entre els blocs funcionals. Hi haurà alguns blocs d’entrada i sortida que ens permeten unir CPLD amb el món extern. A continuació es mostra l’arquitectura de CPLD.

En general, el FB programable s'assembla a matriu de portes lògiques , on es pot programar una matriu de portes AND i les portes OR són estables. Però, cada fabricant té la seva manera de pensar per dissenyar el bloc funcional. Es pot trobar un o / p llistat operant els senyals de retroalimentació obtinguts des de les sortides de la porta OR.

Arquitectura CPLD

A la programació CPLD, el disseny es codifica primer en llenguatge Verilog o VHDL una vegada que el codi (simulat i sintetitzat. Durant la síntesi, es tria el model CPLD (dispositiu de destinació) i es produeix una llista de xarxes de mapes basades en tecnologia. Aquesta llista es pot tancar -adaptar-se a l’arquitectura CPLD genuïna mitjançant un procés de lloc i ruta, que normalment s’aconsegueix amb el programari de lloc i ruta del propietari de CPLD Company. A continuació, l’operador farà alguns processos de confirmació. Si tot és bo, utilitzarà el CPLD, en cas contrari ho reordenarà.

Problemes d'arquitectura de CPLD

Quan es considera un dispositiu lògic programable complex per al seu ús en disseny, hi ha alguns problemes arquitectònics següents que es poden tenir en compte

- La tecnologia de programació

- La capacitat del bloc de funcions

- La capacitat d'E / S

Algunes de les famílies de CPLD de diferents minoristes inclouen

- Altera MAX 7000 i MAX 9000 famílies

- Famílies ATM i ATV Atmel

- Lattice isp família LSI

- Xarxa (Vantis) família MACH

- Família Xilinx XC9500

Famílies de CPLD

Aplicacions de CPLD

Les aplicacions dels CPLD inclouen el següent

- Els complexos dispositius lògics programables són ideals per a aplicacions de control crític d’alt rendiment.

- CPLD es pot utilitzar en dissenys digitals per realitzar les funcions del carregador d’arrencada

- CPLD s’utilitza per carregar les dades de configuració d’una matriu de portes programables de camp des de memòria no volàtil.

- En general, s’utilitzen en aplicacions de disseny petites com la descodificació d’adreces

- Els CPLD s’utilitzen freqüentment en moltes aplicacions, com ara en dispositius portàtils que funcionen amb bateries i que són sensibles al cost, a causa de la seva petita mida i l’ús de poca potència.

Per tant, es tracta d’arquitectura complexa de dispositius lògics programables i de les seves aplicacions. Esperem que tingueu una millor comprensió d’aquest concepte. A més, qualsevol consulta sobre aquest concepte o implementar qualsevol projecte elèctric i electrònic Si us plau, doneu els vostres valuosos suggeriments comentant a la secció de comentaris a continuació. Aquí teniu una pregunta, quina diferència hi ha entre CPLD i FPGA?

Crèdits fotogràfics:

- CPLD wikimedia

- Arquitectura de CPLD slidesharecdn

![4 circuits simples de commutació de palmes [Provat]](https://electronics.jf-parede.pt/img/4017-ic-circuits/21/4-simple-clap-switch-circuits.png)