Als circuits combinacionals, s’utilitzen diferents portes lògiques per dissenyar codificadors, multiplexors, descodificadors i desmultiplexors. Aquests circuits tenen algunes característiques, com la sortida d’aquest circuit, que depèn principalment dels nivells que hi ha als terminals d’entrada en qualsevol moment. Aquest circuit no inclou cap memòria. L’estat anterior de l’entrada no té cap influència en l’estat actual d’aquest circuit. Les entrades i sortides d’un circuit combinacional són ‘n’ núm. d’entrades i ‘m’ núm. de sortides. Alguns dels circuits combinatius són mig sumador i sumador complet, restador, codificador, descodificador, multiplexor i demultiplexador. En aquest article es descriu una visió general de la mitja sumadora i la sumadora completa i funciona amb taules de veritat.

Què és un sumador?

Un sumador és un circuit lògic digital en electrònica que s’utilitza àmpliament per a l’addició de nombres. En molts ordinadors i altres tipus de processadors, els adders fins i tot s’utilitzen per calcular adreces i activitats relacionades i calcular índexs de taula a l’ALU i fins i tot s’utilitzen en altres parts dels processadors. Aquests es poden construir per a moltes representacions numèriques com l'excés-3 o el codi binari decimal. Els sumadors es classifiquen bàsicament en dos tipus: Sumador mitjà i Sumador complet.

Què és el circuit de mig sumador i complet de sumador?

El circuit de mitja sumadora té dues entrades: A i B, que sumen dos dígits d’entrada i generen una suma i una suma. El circuit sumador complet té tres entrades: A i C, que sumen tres números d’entrada i generen una suma i una suma. En aquest article es proporciona informació detallada sobre quin és el propòsit d’un mitjà sumador i sumador complet en formes tabulars i fins i tot en diagrames de circuits. Ja s’esmenta que el propòsit principal i crucial dels sumadors és l’addició. A continuació es detallen els detalls teoria de la mitja sumadora i de la suma completa.

Mitja sumadora bàsica i sumadora completa

Mig vipera

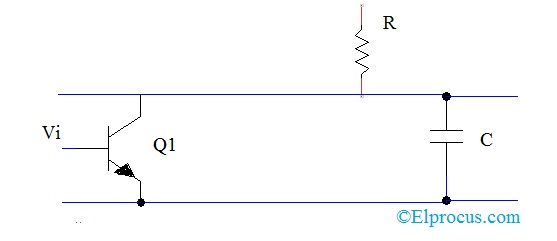

Per tant, arribant a l’escenari de mitja sumadora, afegeix dos dígits binaris on els bits d’entrada s’anomenen augend i addend i el resultat serà dues sortides una és la suma i l’altra és carry. Per realitzar l'operació de suma, XOR s'aplica a les dues entrades i la porta AND s'aplica a les dues entrades per produir carry.

Diagrama funcional HA

Mentre que al circuit de sumador complet, afegeix 3 números d’un bit, on dos dels tres bits es poden anomenar operands i l’altre s’anomena bit portat. La sortida produïda és de 2 bits i es pot referir a aquests a com a sortida i suma.

Mitjançant l'ús d'un mitjà sumador, podeu dissenyar una addició senzilla amb l'ajut de portes lògiques.

Vegem un exemple d'afegir dos bits individuals.

El de 2 bits taula de veritat mitja vipera és el següent:

Taula de veritat de mitja vipera

0 + 0 = 0

0 + 1 = 1

1 + 0 = 1

1 + 1 = 10

Aquestes són les combinacions d’un sol bit que són el mínim possible. Però el resultat per a 1 + 1 és 10, el resultat de la suma s'ha de tornar a escriure com a sortida de 2 bits. Així, les equacions es poden escriure com

0 + 0 = 00

0 + 1 = 01

1 + 0 = 01

1 + 1 = 10

La sortida '1' de '10' es realitza. 'SUM' és la sortida normal i 'CARRY' és la sortida.

Ara s’ha esborrat que es pot implementar fàcilment un sumador d’1 bit amb l’ajut de la porta XOR per a la sortida ‘SUM’ i una porta AND per al ‘transport’.

Per exemple, quan cal afegir dos bytes de 8 bits junts, es pot implementar mitjançant un circuit lògic de sumador complet. El mitjà sumador és útil quan voleu afegir quantitats d'un dígit binari.

Una manera de desenvolupar sumadors de dos dígits binaris seria fer una taula de veritat i reduir-la. Quan es vol fer un sumador de tres dígits binaris, l'operació d'addició de mig sumador es realitza dues vegades. De manera similar, quan decidiu fer un sumador de quatre dígits, l'operació es realitza una vegada més. Amb aquesta teoria, era evident que la implementació és senzilla, però el desenvolupament és un procés que requereix molt de temps.

L'expressió més senzilla utilitza la funció OR exclusiva:

Suma = A XOR B

Portar = A I B

Diagrama lògic HA

I una expressió equivalent en termes del bàsic AND, OR i NOT és:

SUMA = A.B + A.B ’

Codi VHDL per a mitja vipera

Entitat ha

Port (a: a STD_LOGIC

b: a STD_LOGIC

sha: out STD_LOGIC

cha: fora STD_LOGIC)

final ha

Arquitectura El comportament del circuit anterior és

començar

sha<= a xor b

no<= a and b

final Conductual

Número IC de mitja sumadora

La implementació del mitjà sumador es pot fer a través de circuits integrats de lògica digital CMOS d'alta velocitat com la sèrie 74HCxx que inclou el SN74HC08 (7408) i SN74HC86 (7486).

Limitacions de mitja vipera

La raó principal per anomenar aquests sumadors binaris com Half Adders és que no hi ha un rang per incloure el bit de transport mitjançant un bit anterior. Per tant, aquesta és una de les principals limitacions dels HA un cop utilitzats com a sumador binari, particularment en situacions en temps real que impliquen afegir diversos bits. Per tant, aquesta limitació es pot superar utilitzant els sumadors complets.

Sumador complet

Aquest sumador és difícil d’implementar si es compara amb el mitjà sumador.

Diagrama funcional de sumador complet

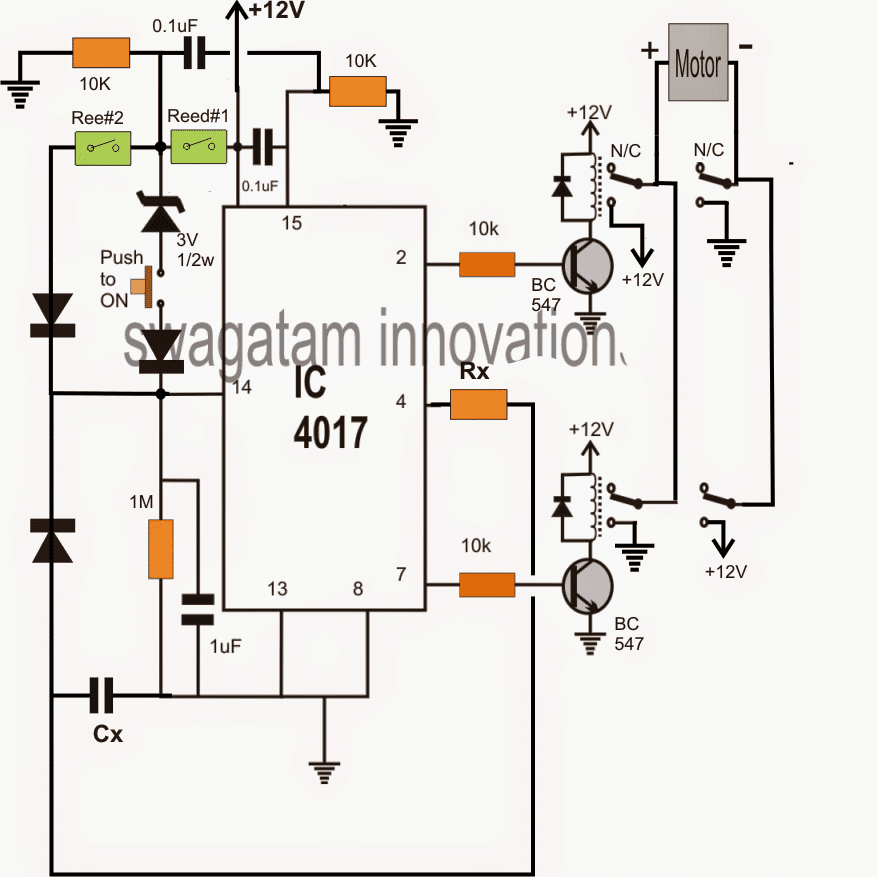

La diferència entre un sumador mitjà i un sumador complet és que el sumador complet té tres entrades i dues sortides, mentre que el mig sumador només té dues entrades i dues sortides. Les dues primeres entrades són A i B i la tercera entrada és una transmissió d’entrada com a C-IN. Quan es dissenya una lògica de sumador complet, encaixa vuit d'ells per crear un sumador de tot un byte i fer que el bit de transport passi d'un sumador al següent.

FA Taula de la Veritat

El transport de sortida es designa com C-OUT i la sortida normal es representa com S que és 'SUM'.

Amb l’anterior taula de veritat de sumador complet , la implementació d'un circuit complet de sumador es pot entendre fàcilment. La SUM 'S' es produeix en dos passos:

- Mitjançant XOR les entrades proporcionades 'A' i 'B'

- El resultat de A XOR B és XORed amb el C-IN

Això genera SUM i C-OUT només és cert quan qualsevol de les tres entrades és ALTA, llavors la C-OUT serà ALTA. Per tant, podem implementar un circuit complet de sumador amb l’ajut de dos circuits de mitja sumadora. Inicialment, el mitjà sumador s’utilitzarà per afegir A i B per produir una suma parcial i es pot utilitzar una lògica de sumador de la segona meitat per afegir C-IN a la suma produïda pel primer mitjà sumador per obtenir la sortida S final.

Si alguna de les lògiques de mitja sumadora produeix un transport, hi haurà un transport de sortida. Per tant, C-OUT serà una funció OR de les sortides Carry de mig sumador. Mireu la implementació del circuit complet de sumadors que es mostra a continuació.

Diagrama lògic de sumador complet

La implementació de diagrames lògics més grans és possible amb la lògica de sumador complet anterior, un símbol més simple s'utilitza principalment per representar l'operació. A continuació es mostra una representació esquemàtica més senzilla d’un sumador complet d’un bit.

Amb aquest tipus de símbol, podem afegir dos bits junts, prenent una portada del següent ordre de magnitud inferior i enviant una portada al següent ordre de magnitud superior. En un ordinador, per a una operació de diversos bits, cada bit ha d’estar representat per un sumador complet i s’ha d’afegir simultàniament. Per tant, per afegir dos números de 8 bits, necessitareu 8 sumadors complets que es poden formar en cascada de dos dels blocs de 4 bits.

Mitja sumadora i sumadora completa amb K-Map

Fins i tot la suma i els resultats de la meitat del sumador també es poden obtenir amb el mètode del mapa de Karnaugh (mapa K). El expressió booleana mig sumador i sumador complet es pot obtenir a través de K-map. Per tant, el mapa K d’aquests sumadors es discuteix a continuació.

El mig K-mapa és

Mapa K HA

El sumador complet K-Map és

FA K-Mapa

Expressió lògica de SUM i Carry

L'expressió lògica de suma (S) es pot determinar en funció de les entrades esmentades a la taula.

= A’B’Cin + A ’B CCin’ + A B’Cin ’+ AB Cin

= Cin (A’B ’+ AB) + Cin’ (A’B + A B ’)

= Cin EX-OR (A EX-OR B)

= (1,2,4,7)

L'expressió lògica del carry (Cout) es pot determinar en funció de les entrades esmentades a la taula.

= A’B Cin + AB’Cin + AB Cin ’+ ABCin

= AB + BCin + ACin

= (3, 5, 6, 7)

Amb les taules de veritat esmentades, es poden obtenir els resultats i el procediment és:

Un circuit combinacional combina les diferents portes del circuit on poden ser codificador, descodificador, multiplexor i demultiplexor . Les característiques dels circuits combinacionals són les següents.

- La sortida en qualsevol moment es basa només en els nivells que hi ha als terminals d’entrada.

- No utilitza cap memòria. L'estat d'entrada anterior no té cap efecte sobre l'estat actual del circuit.

- Pot tenir qualsevol nombre d'entrades i m nombre de sortides.

Codificació VHDL

Codificació VHDL per al sumador complet inclou el següent.

entitat full_add és

Port (a: a STD_LOGIC

b: a STD_LOGIC

cin: a STD_LOGIC

suma: fora STD_LOGIC

cout: fora STD_LOGIC)

acabar full_add

Arquitectura El comportament de full_add és

component ha és

Port (a: a STD_LOGIC

b: a STD_LOGIC

sha: out STD_LOGIC

cha: fora STD_LOGIC)

component final

senyal s_s, c1, c2: STD_LOGIC

començar

HA1: mapa de ports ha (a, b, s_s, c1)

HA2: mapa de ports ha (s_s, cin, suma, c2)

cost<=c1 or c2

final Conductual

El diferència entre mig sumador i sumador complet és que mig sumador produeix resultats i el sumador complet utilitza mig sumador per produir algun altre resultat. De la mateixa manera, si bé el Sumador Complet és de dos Mitges Sumadors, el Sumador Complet és el bloc real que fem servir per crear els circuits aritmètics.

Porteu additius Lookahead

En el concepte de circuits de sumador de càrrega ondulada, els bits necessaris per a l'addició estan disponibles immediatament. Mentre que cada secció de sumadors ha de conservar el seu temps per a l'arribada del transport del bloc de sumadors anterior. Per això, es necessita més temps per produir SUM i CARRY, ja que cada secció del circuit espera l'arribada de l'entrada.

Per exemple, per lliurar la sortida del novè bloc, ha de rebre l'entrada del bloc (n-1). I aquest retard es correspon amb el nom de retard de propagació.

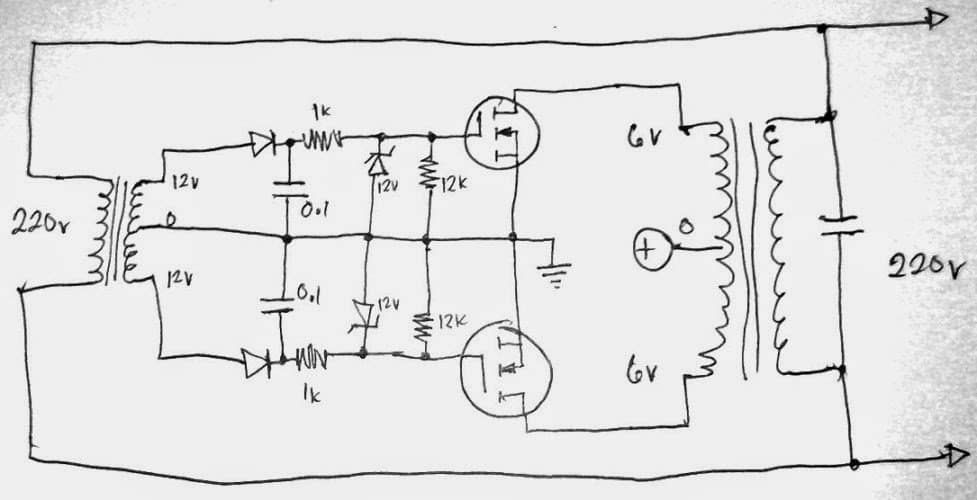

Per superar el retard en el sumador de les ondulacions, es va introduir un sumador que porta la mirada. Aquí, mitjançant l’ús de maquinari complicat, es pot minimitzar el retard de propagació. El diagrama següent mostra un sumador de capçalera que utilitza sumes completes.

Porteu Lookahead fent servir el sumador complet

La taula de veritat i les equacions de sortida corresponents són

| A | B | C | C +1 | Condició |

| 0 | 0 | 0 | 0 | Sense portar Generar |

| 0 | 0 | 1 | 0 | |

| 0 | 1 | 0 | 0 | |

| 0 | 1 | 1 | 1 | Sense portar Propagar |

| 1 | 0 | 0 | 0 | |

| 1 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 1 | Porteu Generar |

| 1 | 1 | 1 | 1 |

L’equació de propagació de la càrrega és Pi = Ai XOR Bi i la generació de la càrrega és Gi = Ai * Bi. Amb aquestes equacions, les equacions de suma i de transport es poden representar com

SUMA = Pi XOR Ci

Ci + 1 = Gi + Pi * Ci

Gi només ofereix un transport quan les entrades Ai i Bi són 1 sense tenir en compte el transport d’entrada. Pi està relacionat amb la propagació del transport de Ci a Ci + 1.

Diferència entre mig sumador i sumador complet

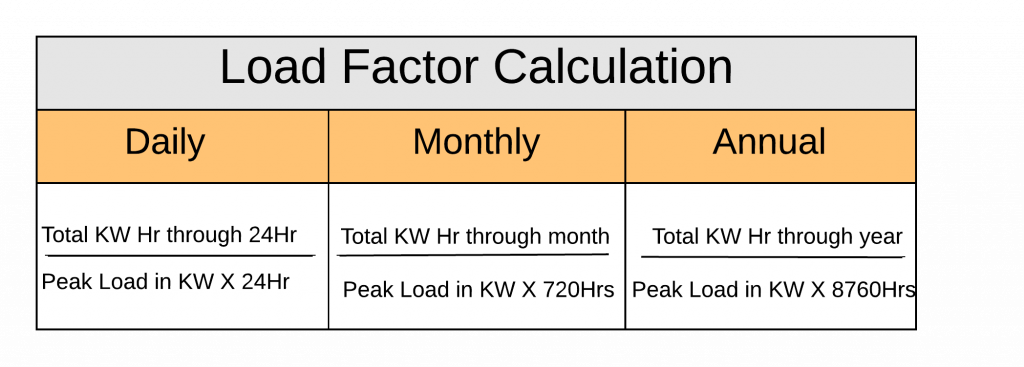

El diferència entre la taula de sumador mitjà i el sumador complet es mostra a continuació.

| Mig vipera | Sumador complet |

| Half Adder (HA) és un circuit lògic combinacional i aquest circuit s’utilitza per afegir dos dígits d’un bit. | Full Adder (FA) és un circuit combinacional i aquest circuit s’utilitza per afegir tres dígits d’un bit. |

| A HA, un cop generat el transport a partir de l’addició anterior no es pot afegir al pas següent. | A FA, un cop es genera el transport a partir de l’addició anterior, es pot afegir al següent pas. |

| El mig sumador inclou dues portes lògiques com la porta AND i la porta EX-OR. | El sumador complet inclou dues portes EX-OR, dues portes OR i dues portes AND. |

| Els bits d'entrada al mitjà sumador són dos com A, B. | Els bits d'entrada del sumador complet són tres com A, B i C-in |

| La meitat de sumador suma i l’equació de transport és S = a⊕b C = a * b | L’expressió lògica de sumador complet és S = a ⊕ b⊕Cin Cout = (a * b) + (Cin * (a⊕b)). |

| El HA s’utilitza en ordinadors, calculadores, dispositius per a la mesura digital, etc. | FA s'utilitza en processadors digitals, addició de múltiples bits, etc. |

El diferències clau entre el mitjà sumador i el sumador complet es comenten a continuació.

- El mitjà sumador genera sum & carry afegint dues entrades binàries, mentre que el sumador complet s’utilitza per generar sum & carry afegint tres entrades binàries. Tant l'arquitectura de maquinari de mitja sumadora com de sumadora completa no és la mateixa.

- La característica principal que diferencia HA i FA és que a HA no hi ha cap acord que tingui en compte que la darrera incorporació és la seva entrada. Però, un FA localitza una columna d’entrada concreta com Cin per considerar el bit de transport de l’última addició.

- Els dos sumadors mostraran una diferència en funció dels components utilitzats al circuit per a la seva construcció. Els mig sumadors (HA) estan dissenyats amb la combinació de dues portes lògiques com AND & EX-OR, mentre que la FA està dissenyada amb la combinació de tres portes AND, dues XOR i una OR.

- Bàsicament, les HA funcionen en dues entrades d’1 bit, mentre que les FA funcionen en tres entrades d’1 bit. El mitjà sumador s'utilitza en diferents dispositius electrònics per avaluar l'addició, mentre que el sumador complet s'utilitza en processadors digitals per afegir un bit llarg.

- Les similituds d’aquests dos sumadors són, ambdós HA i FA són circuits digitals combinacionals, de manera que no fan servir cap element de memòria com els circuits seqüencials. Aquests circuits són essencials per a l'operació aritmètica per proporcionar l'addició del nombre binari.

Implantació completa de sumadors mitjançant mitges sumadores

La implementació d'un FA es pot fer a través de dos mitges sumadores que es connecten lògicament. A continuació es pot mostrar el diagrama de blocs que indica la connexió d’un FA mitjançant dos mitges sumadores.

La suma i les equacions de càlculs anteriors són

S = A ‘B’ Cin + A ’BC’ a + ABCin

Cout = AB + ACin + BCin

L'equació suma es pot escriure com.

Cin (A’B ‘+ AB) + C’ a (A ‘B + A B’)

Per tant, Suma = Cin EX-OR (A EX-OR B)

Cin (A EX-OR B) + C’in (A EX-OR B)

= Cin EX-OR (A EX-OR B)

Cout es pot escriure com el següent.

COUT = AB + ACin + BCin.

Cout = AB + + decepcions BCIN (A + A)

= ABCin + AB + ACin + A ’B Cin

= AB (1 + Cin) + ACin + A ’B Cin

= A B + ACin + A ’B Cin

= AB + ACin (B + B ’) + A’ B Cin

= ABCin + AB + A’B Cin + A ’B Cin

= AB (Cin + 1) + A B Cin + A ’B Cin

= AB + AB ’Cin + A’ B Cin

= AB + Cin (AB ’+ A’B)

Per tant, COUT = AB + Cin (A EX-OR B)

Depenent de les dues sumes i equacions de transport anteriors, el circuit FA es pot implementar amb l'ajut de dos HAs i una porta OR. El diagrama de circuits d’un sumador complet amb dos mitges sumadors s’il·lustra més amunt.

Sumador complet amb dues mitges additores

Disseny complet de sumador amb NAND Gates

Una porta NAND és un tipus de porta universal, que s’utilitza per executar qualsevol tipus de disseny lògic. A continuació es mostra el circuit FA amb el diagrama de portes NAND.

FA amb NAND Gates

FA és un sumador fàcil d’un bit i, si volem executar l’addició de n-bit, llavors n no. de FA d'un bit s'han d'utilitzar en format de connexió en cascada.

Avantatges

El avantatges de mig sumador i sumador complet inclou el següent.

- El propòsit principal d'un mitjà sumador és afegir dos números d'un sol bit

- Els sumadors complets tenen la possibilitat d'afegir un bit de transport que és el resultat de l'addició anterior

- Amb el sumador complet, es poden implementar circuits crucials com el sumador, el multiplexor i molts altres

- Els circuits de sumador complet consumeixen una energia mínima

- Els avantatges d’un sumador complet sobre un mitjà sumador són que s’utilitza un sumador complet per superar l’inconvenient d’un mitjà sumador, ja que la meitat de sumador s’utilitza principalment per afegir dos números d’1 bit. La meitat dels sumadors no afegeixen el bit de transport, de manera que per superar aquest sumador complet s’utilitza. A Sumador complet, es pot afegir tres bits i es generen dues sortides.

- El disseny d’adders és senzill i és un element bàsic per tal de comprendre fàcilment l’addició d’un bit.

- Aquest sumador es pot convertir en mig substractor afegint un inversor.

- Mitjançant l'ús d'un sumador complet, es pot obtenir un alt rendiment.

- Alta velocitat

- Molt fort per subministrar l’escala de tensió

Desavantatges

El desavantatges de mig sumador i sumador complet inclou el següent.

- A més, el mitjà sumador no es pot utilitzar abans de portar-lo, de manera que no és aplicable per afegir en cascada l'addició de diversos bits.

- Per superar aquest inconvenient, cal afegir-ne tres a 1 bit.

- Un cop utilitzat el FA en forma de cadena com un RA (Ripple Adder), es pot reduir la capacitat de sortida de la unitat.

Aplicacions

Les aplicacions de mitja sumadora i sumadora completa inclouen el següent.

- L'addició de bits binaris es pot fer per mitjà de sumador mitjançant ALU a l'ordinador perquè utilitza sumador.

- La combinació de mitja sumadora es pot utilitzar per dissenyar un circuit complet de sumador.

- A les calculadores i a la mesura de les adreces, així com de les taules, s’utilitzen mig sumadors

- Aquests circuits s’utilitzen per gestionar diferents aplicacions dins de circuits digitals. En el futur, tindrà un paper clau en l’electrònica digital.

- Un circuit FA s'utilitza com a element en molts circuits grans com Ripple Carry Adder. Aquest sumador afegeix el nombre de bits simultàniament.

- Les FA s’utilitzen a la Unitat Lògica Aritmètica (ALU)

- Les FA s’utilitzen en aplicacions relacionades amb gràfics com la GPU (Graphics Processing Unit)

- Aquests s’utilitzen al circuit de multiplicació per executar la multiplicació Carryout.

- En un ordinador, per generar l'adreça de memòria i construir el contrapunt del programa cap a instruccions posteriors, s'utilitza la Unitat lògica aritmètica mitjançant Full Adders.

Així, sempre que es fa l'addició de dos nombres binaris, els dígits s'afegeixen al principi els bits mínims. Aquest procés es pot realitzar mitjançant un mitjà sumador, ja que és el n / n més senzill que permet afegir dos números de 1 bit. Les entrades d’aquest sumador són els dígits binaris, mentre que les sortides són la suma (S) i el transport (C).

Sempre que s’inclou el nombre de dígits, la xarxa HA s’utilitza simplement per connectar el mínim de dígits, ja que l’HA no pot afegir el número de transport de la classe anterior. Un sumador complet es pot definir com la base de tots els dispositius aritmètics digitals. S'utilitza per afegir tres números d'un dígit. Aquest sumador inclou tres entrades com A, B i Cin, mentre que les sortides són Sum i Cout.

Conceptes relacionats

El conceptes relacionats amb el mitjà sumador i el sumador complet simplement no s’adhereixen a un sol propòsit. Tenen un ús extensiu en moltes aplicacions i es mencionen alguns dels relacionats:

- Número de mig sumador i sumador complet

- Desenvolupament de sumadors de 8 bits

- Quines són les precaucions per al mitjà de sumador?

- Applet JAVA d'un escumador Ripple Carry

Per tant, es tracta de teoria de la mitja sumadora i de la suma completa juntament amb les taules de veritat i els diagrames lògics, també es mostra el disseny del sumador complet mitjançant circuit de mitja sumadora. Molts dels mig sumador i sumador complet pdf hi ha documents disponibles per proporcionar informació avançada sobre aquests conceptes. A més, és important saber-ho com s’implementa un sumador complet de 4 bits ?