Aquest article explica el generació de modulació d'amplada de pols senyals amb cicle de treball variable en FPGA mitjançant VHDL. PWM té una freqüència fixa i un voltatge variable. En aquest article també es parla del Gestor de rellotges digitals per reduir la freqüència del rellotge reduint la desviació del senyal del rellotge. S'utilitza una freqüència fixa per produir les dades d'entrada que produeixen els senyals PWM mitjançant un comparador. Les empreses electròniques dissenyen el maquinari dedicat als seus productes amb els seus estàndards i protocols, cosa que fa que sigui difícil per als usuaris finals reconfigurar el maquinari segons les seves necessitats. Aquest requisit de maquinari va conduir al creixement d'un nou segment de configuració per al client circuits integrats programables de camp anomenats FPGA .

Modulació d'amplada de pols (PWM)

La modulació de l'amplada de pols s'utilitza àmpliament en aplicacions de comunicació i sistemes de control . La modulació de l'amplada de pols es pot generar utilitzant diferents enfocaments en sistemes de control. Aquí, en aquest article, PWM es genera mitjançant el llenguatge de descripció de maquinari (VHDL) i s’implementa a FPGA. La implementació de PWM a FPGA pot processar les dades més ràpidament i l'arquitectura del controlador es pot optimitzar per a espai o velocitat.

PWM és una tècnica per proporcionar lògica '0' i lògica '1' durant un període de temps controlat. És una font de senyal que implica la modulació del seu cicle de treball per controlar la quantitat d'energia enviada a la càrrega. A PWM, el període de temps de l’ona quadrada es manté constant i el temps durant el qual el senyal es manté ALT és variat.

El PWM genera els impulsos de la seva sortida de manera que el valor mitjà de HIGHs i LOWs sigui proporcional a l'entrada PWM. El cicle de treball del senyal es pot variar. Un senyal PWM és una ona quadrada de període constant amb cicle de treball variable. És a dir, la freqüència del senyal PWM és constant, però el període de temps del senyal es manté elevat i varia segons es mostra.

Senyal PWM

VHDL

VHDL és un llenguatge utilitzat per descriure el comportament de dissenys de circuits digitals . El VHDL és utilitzat per indústries i acadèmics amb la finalitat de simular circuits digitals. El seu disseny es pot simular i traduir en la forma adequada per a la implementació en maquinari.

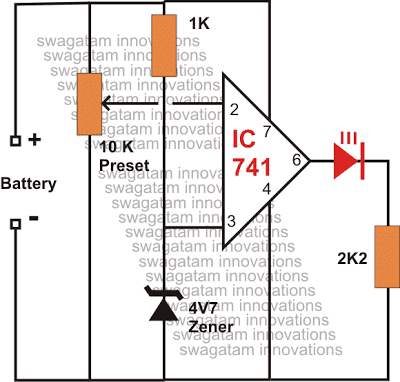

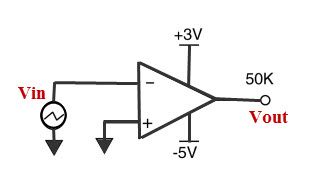

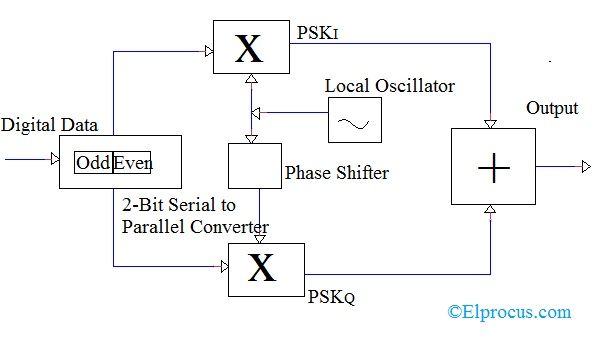

Arquitectura PWM

Per produir les dades d'entrada per generar el PWM mitjançant un comptador d'execució lliure de N-bits d'alta velocitat, la sortida del qual es compara amb la sortida del registre i emmagatzema el cicle de treball d'entrada desitjat amb l'ajut del comparador. El comparador la sortida s'estableix a 1 quan tots dos valors són iguals. Aquesta sortida del comparador s'utilitza per configurar el tancament RS. El senyal de desbordament del comptador s’utilitza per restablir el tancament RS. El sortida del pestell RS dóna la sortida PWM desitjada. Aquest senyal de desbordament també s’utilitza per carregar un nou cicle de treball de N bits al registre. PWM té una freqüència fixa i un voltatge variable. Aquest valor de tensió canvia de 0V a 5 V.

Senyal PWM amb cicle de treball variable

El PWM bàsic genera els senyals, que dóna la sortida de PWM, requereix un comparador que compare entre dos valors. El primer valor representa el senyal quadrat generat pel comptador de bits N i el segon valor representa el senyal quadrat que conté la informació sobre el cicle de treball. El comptador genera el senyal de càrrega sempre que hi ha un desbordament. Un cop el senyal de càrrega s’activa, el registre carrega el nou valor del cicle de treball. El senyal de càrrega també s’utilitza per restablir el pestell. La sortida de bloqueig és un senyal PWM. Això pot variar amb el canvi del valor del cicle de treball.

Què és FPGA?

El FPGA és un camp de portes programable al camp. És un tipus de dispositiu que s’utilitza àmpliament en circuits electrònics. Els FPGA ho són dispositius semiconductors que contenen blocs lògics programables i circuits d’interconnexió. Es pot programar o reprogramar a la funcionalitat requerida després de la fabricació.

FPGA

Conceptes bàsics de FPGA

Quan es fabrica una placa de circuit i si conté un FPGA com a part d’ella. Es programa durant el procés de fabricació i es pot reprogramar posteriorment per crear una actualització o fer els canvis necessaris. Aquesta característica de FPGA el fa únic a ASIC. Els circuits integrats específics d'aplicació (ASIC) es fabriquen a mida per a tasques de disseny específiques. En els passats FPGA s’utilitzaven per desenvolupar una velocitat, complexitat i disseny de volum baixos, però avui en dia FPGA pujarà fàcilment la barrera de rendiment fins a 500 MHz.

Als microcontroladors, el xip està dissenyat per a un client i ha d’escriure el programari i compilar-lo al fitxer hexadecimal per carregar-lo al microcontrolador. Aquest programari es pot substituir fàcilment ja que s’emmagatzema a la memòria flash. Als FPGA, no hi ha cap processador per executar el programari i nosaltres som els que dissenyem el circuit. Podem configurar un FPGA tan simple com una porta AND o un complex com un processador multi-core. Per crear un disseny, escrivim el llenguatge de descripció de maquinari (HDL), que és de dos tipus: Verilog i VHDL. A continuació, l'HDL se sintetitza en un fitxer de bits mitjançant un BITGEN per configurar el FPGA. El FPGA emmagatzema la configuració a la RAM, és a dir, la configuració es perd quan no hi ha connectivitat d’alimentació. Per tant, s'han de configurar cada vegada que es subministra energia.

Arquitectura de FPGA

Els FPGA són xips de silici prefabricats que es poden programar elèctricament per implementar dissenys digitals. El primer FPGA basat en memòria estàtica anomenat SRAM s’utilitza per configurar tant la lògica com la interconnexió mitjançant un flux de bits de configuració. L’actual EPGA actual conté aproximadament 3.30.000 blocs lògics i al voltant de 1.100 entrades i sortides.

Arquitectura FPGA

L'arquitectura de FPGA consta de tres components principals

- Blocs lògics programables, que implementen funcions lògiques

- Encaminament programable (interconnexions), que implementa funcions

- Blocs d'E / S, que s'utilitzen per fer connexions fora de xip

Aplicacions de senyals PWM

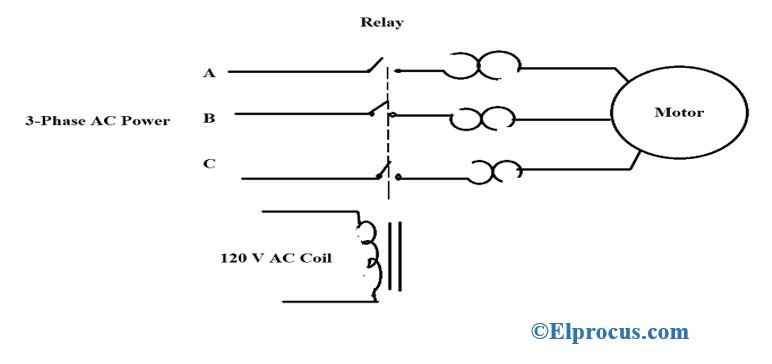

Els senyals PWM s’utilitzen àmpliament per a aplicacions de control. Com controlar motors de corrent continu, vàlvules de control, bombes, hidràulica, etc. Aquí hi ha les poques aplicacions dels senyals PWM.

- Sistemes de calefacció amb temps lent de 10 a 100Hz o superior.

- Motors elèctrics de corrent continu de 5 a 10 KHz

- Fonts d’alimentació o amplificadors d’àudio de 20 a 200 KHz.

Aquest article tracta sobre el generació de senyals PWM amb cicle de treball variable mitjançant FPGA. A més, per a qualsevol ajuda sobre projectes electrònics o dubtes sobre aquest article, podeu contactar amb nosaltres comentant la secció de comentaris que es mostra a continuació.