En aquest post anem a entendre de forma exhaustiva quant són les portes lògiques i el seu funcionament. Farem un cop d'ull a la definició bàsica, símbol, taula de veritat, portes d'entrada múltiples, també construirem equivalents de portes basades en transistors i, finalment, farem una visió general de diversos IC CMOS rellevants.

Què són Logic Gates

Una porta lògica en un circuit electrònic es pot expressar com una unitat física representada mitjançant una funció booleana.

En altres paraules, una porta lògica està dissenyada per executar una funció lògica mitjançant entrades binàries simples o més i per generar una única sortida binària.

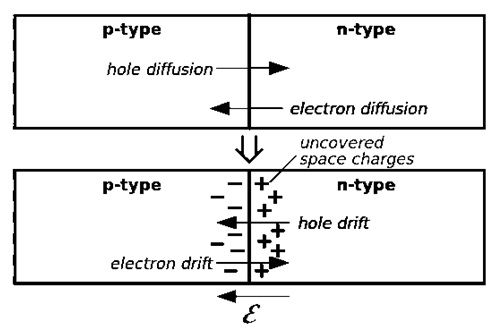

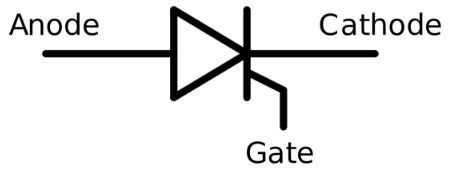

Les portes lògiques electròniques es configuren i s’implementen fonamentalment mitjançant blocs de semiconductors o elements com ara díodes o transistors que funcionen com a commutadors ON / OFF amb un patró de commutació ben definit. Les portes lògiques faciliten la cascada de les portes de manera que permeten fàcilment la composició de funcions booleanes, cosa que permet crear models físics de tota la lògica booleana. Això permet, a més, escriure algorismes i matemàtiques mitjançant la lògica booleana.

Els circuits lògics poden emprar elements semiconductors en la gamma de multiplexors, registres, unitats lògiques aritmètiques (ALU) i memòria informàtica, i fins i tot microprocessadors, que impliquen fins a 100 milions de portes lògiques. En la implementació actual, trobareu principalment transistors d’efecte de camp (FET), que s’utilitzen per a la fabricació de portes lògiques, un bon exemple són els transistors d’efecte de camp de metall-òxid-semiconductor o MOSFET.

Comencem el tutorial amb lògica I portes.

Què és Logic 'AND' Gate?

És una porta electrònica, la sortida de la qual es converteix en 'alta' o '1' o 'veritable' o emet un 'senyal positiu' quan totes les entrades de les portes AND són 'altes' o '1' o 'veritables' o ' senyal positiu ”.

Per exemple: Digueu en una porta AND amb el número 'n' d'entrades, si totes les entrades són 'altes' la sortida es torna 'alta'. Fins i tot si una entrada és 'BAIX' o '0' o 'fals' o 'senyal negatiu', la sortida es converteix en 'BAIX' o '0' o 'fals' o emet un 'senyal negatiu'.

Nota:

Els termes 'alt', '1', 'senyal positiu' i 'veritable' són essencialment el mateix (el senyal positiu és el senyal positiu de la bateria o de la font d'alimentació).

Els termes 'BAIX', '0', 'senyal negatiu' i 'fals' són essencialment el mateix (el senyal negatiu és el senyal negatiu de la bateria o de la font d'alimentació).

Il·lustració del símbol Logic AND Gate:

Aquí la “A” i la “B” són les dues entrades i la sortida “Y”.

L’expressió booleana de la porta lògica AND: la sortida ‘Y’ és la multiplicació de les dues entrades ‘A’ i ‘B’. (A.B) = Y.

La multiplicació booleana es denota amb un punt (.)

Si 'A' és '1' i 'B' és '1' la sortida és (A.B) = 1 x 1 = '1' o 'alta'

Si 'A' és '0' i 'B' és '1' la sortida és (A.B) = 0 x 1 = '0' o 'Baixa'

Si 'A' és '1' i 'B' és '0' la sortida és (A.B) = 1 x 0 = '0' o 'Baixa'

Si 'A' és '0' i 'B' és '0' la sortida és (A.B) = 0 x 0 = '0' o 'Baixa'

Les condicions anteriors es simplifiquen a la taula de veritat.

Taula de veritat (dues entrades):

| A (entrada) | B (INPUT) | Y (sortida) |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Porta d'entrada 'I' de 3 entrades:

Il·lustració de 3 entrades i portes:

Les portes lògiques i AND poden tenir un nombre ‘n’ d’entrades, el que significa que pot tenir més de dues entrades (les portes lògiques I tindran almenys dues entrades i sempre una sortida).

Per a una porta AND de 3 entrades, l'equació booleana gira així: (A.B.C) = Y, de manera similar per a 4 entrades i més.

Taula de veritat per a una lògica d'entrada I porta:

| A (INPUT) | B (INPUT) | C (INPUT) | S (SORTIDA) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

Lògica d'entrada múltiple I portes:

Les portes Logic AND comercials només estan disponibles en 2, 3 i 4 entrades. Si tenim més de 4 entrades, hem de posar en cascada les portes.

Podem tenir sis portes AND lògiques d’entrada en cascada de les dues portes AND d’entrada de la següent manera:

Ara l’equació booleana del circuit anterior es converteix en Y = (A.B). (C.D). (E.F)

Tot i això, totes les regles lògiques esmentades s'apliquen al circuit anterior.

Si utilitzeu només 5 entrades de les 6 portes AND anteriors, podem connectar una resistència pull-up a qualsevol pin i ara es converteix en 5 porta AND.

Porta lògica i entrada basada en dos transistors:

Ara ja sabem, com funciona una porta lògica AND, construïm una porta AND de 2 entrades mitjançant dos transistors NPN. Els CI lògics es construeixen gairebé de la mateixa manera.

Esquema de dos transistors i portes:

A la sortida “Y” podeu connectar un LED si la sortida és alta, el LED brillarà (terminal LED + Ve a “Y” amb una resistència de 330 ohm i negatiu a GND).

Quan apliquem un senyal alt a la base dels dos transistors, tots dos transistors s’encenen, el senyal + 5V estarà disponible a l’emissor del T2, de manera que la sortida es convertirà en alta.

Si algun dels transistors està DESACTIVAT, no hi haurà tensió positiva a l’emissor de T2, però a causa de la resistència d’arrencada de 1 K, la tensió negativa estarà disponible a la sortida, de manera que la sortida es coneix com a baixa.

Ara ja saps construir lògica I porta pròpia.

Quad I porta IC 7408:

Si voleu comprar lògica I porta del mercat, obtindreu la configuració anterior.

Té 14 pins, el pin # 7 i el pin # 14 són GND i Vcc respectivament. Funciona a 5V.

Retard de propagació:

El retard de propagació és el temps que triga la sortida a canviar de BAIX a ALT i viceversa.

El retard de propagació de BAIX a ALT és de 27 nanosegons.

El retard de propagació d’ALTA a BAIXA és de 19 nanosegons.

Altres IC de porta 'I' disponibles habitualment:

• 74LS08 Quad 2 entrades

• 74LS11 Triple 3 entrades

• 74LS21 Dual de 4 entrades

• CD4081 Quad 2 entrades

• CD4073 Triple 3 entrades

• CD4082 Dual de 4 entrades

Sempre podeu consultar el full de dades dels CI anteriors per obtenir més informació.

Com funciona la lògica funció 'exclusiva NOR'

En aquest post explorarem la porta lògica 'Ex-NOR' o la porta exclusiva-NOR. Farem una ullada a la definició bàsica, símbol, taula de veritat, circuit equivalent Ex-NOR, utilització de la realització Ex-NOR lògica portes NAND i, finalment, farem una descripció general de la porta Ex-OR IC 74266 de l'entrada de quad 2.

Què és la porta 'NOR exclusiva'?

És una porta electrònica, la sortida de la qual es converteix en 'alta' o '1' o 'veritable' o emet un 'senyal positiu' quan les entrades són nombre parell de '1s' lògic (o 'veritable' o 'alt' o ' senyal positiu ”).

Per exemple: Digueu una porta NOR exclusiva amb un nombre d’entrades ‘n’, si les entrades són lògiques “HIGH” amb 2 o 4 o 6 entrades (nombre parell d’entrada “1s”) la sortida es converteix en “HIGH”.

Fins i tot si no apliquem cap lògica 'alta' als pins d'entrada (és a dir, el nombre zero de la lògica 'HIGH' i tota la lògica 'BAIXA), encara' zero 'és un número parell la sortida es converteix en' HIGH '.

Si el nombre de '1s' lògics aplicats és imparell, la sortida es convertirà en 'BAIX' (o '0' o 'fals' o 'senyal negatiu').

Això és oposat a la porta lògica 'OR exclusiu', on la seva sortida es converteix en 'ALTA' quan les entrades tenen un nombre imparell de lògica '1s'.

Nota:

Els termes 'alt', '1', 'senyal positiu' i 'veritable' són essencialment el mateix (el senyal positiu és el senyal positiu de la bateria o de la font d'alimentació).

Els termes 'BAIX', '0', 'senyal negatiu' i 'fals' són essencialment el mateix (el senyal negatiu és el senyal negatiu de la bateria o de la font d'alimentació).

Il·lustració de la porta Logic 'Exclusive NOR':

Circuit equivalent a porta 'NOR exclusiva':

L'anterior és el circuit equivalent per a la lògica Ex-NOR, que és bàsicament una combinació de porta lògica 'OR exclusiu' i porta lògica 'NO'.

Aquí la “A” i la “B” són les dues entrades i la sortida “Y”.

L’expressió booleana per a la porta lògica Ex-NOR: Y = (AB) ̅ + AB.

Si 'A' és '1' i 'B' és '1' la sortida és ((AB) ̅ + AB) = 0 + 1 = '1' o 'HIGH'

Si 'A' és '0' i 'B' és '1' la sortida és ((AB) ̅ + AB) = 0 + 0 = '0' o 'BAIX'

Si 'A' és '1' i 'B' és '0' la sortida és ((AB) ̅ + AB) = 0 + 0 = '0' o 'BAIX'

Si 'A' és '0' i 'B' és '0' la sortida és ((AB) ̅ + AB) = 1 + 1 = '1' o 'HIGH'

Les condicions anteriors es simplifiquen a la taula de veritat.

Taula de veritat (dues entrades):

| A (entrada) | B (INPUT) | Y (sortida) |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Porta NOR exclusiva de 3 entrades:

Il·lustració de la porta Ex-NOR de 3 entrades:

Taula de veritat per a la porta EX-OR de la lògica d'entrada de 3:

| A (INPUT) | B (INPUT) | C (INPUT) | S (SORTIDA) |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Per a la porta Ex-NOR de 3 entrades, l'equació booleana es converteix en: A ̅ (BC) ̅ + ABC ̅ + AB ̅C + A ̅BC.

La porta lògica 'Ex-NOR' no és una porta lògica fonamental, sinó la combinació de diferents portes lògiques. La porta Ex-NOR es pot realitzar utilitzant portes lògiques 'OR', porta lògica 'AND' i porta lògica 'NAND' de la següent manera:

Circuit equivalent per a la porta 'Exclusive NOR':

El disseny anterior té un gran inconvenient, necessitem 3 portes lògiques diferents per fer una porta Ex-NOR. Però podem superar aquest problema implementant la porta Ex-NOR amb només portes lògiques 'NAND', això també és econòmic de fabricar.

Porta NOR exclusiva que utilitza la porta NAND:

Les portes NOR exclusives s’utilitzen per realitzar tasques informàtiques complicades com ara operacions aritmètiques, sumadors binaris, restes binàries, comprovadors de paritat i s’utilitzen com a comparadors digitals.

Logic Exclusive-NOR Gate IC 74266:

Si voleu comprar la porta lògica Ex-NOR del mercat, obtindreu la configuració DIP anterior.

Té 14 pins, el pin # 7 i el pin # 14 són GND i Vcc respectivament. Funciona a 5V.

Retard de propagació:

El retard de propagació és el temps que es triga a canviar la sortida de BAIX a ALT i viceversa després de donar entrada.

El retard de propagació de BAIX a ALT és de 23 nanosegons.

El retard de propagació d’ALTA a BAIXA és de 23 nanosegons.

ICs de porta 'EX-NOR' disponibles habitualment:

74LS266 Quad 2 entrades

CD4077 Quad 2 entrades

Com funciona NAND Gate

A l'explicació següent, explorarem la porta NAND de la lògica digital. Farem un cop d'ull a la definició bàsica, símbol, taula de veritat, porta NAND d'entrada múltiple, construirem una porta NAND basada en transistor de 2 entrades, diverses portes lògiques utilitzant només la porta NAND i, finalment, farem una visió general de la porta NAND IC 7400.

Què és Logic 'NAND' Gate?

És una porta electrònica, la sortida de la qual es converteix en 'BAIX' o '0' o 'fals' o emet un 'senyal negatiu' quan totes les entrades de les portes NAND són 'altes' o '1' o 'veritables' o ' senyal positiu ”.

Per exemple: Digueu una porta NAND amb el nombre 'n' d'entrades, si totes les entrades són 'altes', la sortida es convertirà en 'BAIX'. Fins i tot si una entrada és “BAIX” o “0” o “fals” o “senyal negatiu”, la sortida es torna “ALTA” o “1” o “veritable” o emet un “senyal positiu”.

Nota:

Els termes 'alt', '1', 'senyal positiu' i 'veritable' són essencialment el mateix (el senyal positiu és el senyal positiu de la bateria o de la font d'alimentació).

Els termes 'BAIX', '0', 'senyal negatiu' i 'fals' són essencialment el mateix (el senyal negatiu és el senyal negatiu de la bateria o de la font d'alimentació).

Il·lustració del símbol de la porta NAND de Logic:

Aquí la “A” i la “B” són les dues entrades i la sortida “Y”.

Aquest símbol és la porta 'I' amb inversió 'o'.

Circuit equivalent de la porta lògica 'NAND':

La porta NAND lògica és la combinació de la porta lògica “I” i la porta lògica “NO”.

L’expressió booleana de la porta NAND lògica: la sortida ‘Y’ és la multiplicació complementària de les dues entrades ‘A’ i ‘B’. Y = ((A.B) ̅)

La multiplicació booleana es denota amb un punt (.) I la complementària (inversió) es representa amb una barra (-) sobre una lletra.

Si 'A' és '1' i 'B' és '1' la sortida és ((A.B) ̅) = (1 x 1) ̅ = '0' o 'BAIX'

Si 'A' és '0' i 'B' és '1' la sortida és ((A.B) ̅) = (0 x 1) ̅ = '1' o 'HIGH'

Si 'A' és '1' i 'B' és '0', la sortida és ((A.B) ̅) = (1 x 0) ̅ = '1' o 'HIGH'

Si 'A' és '0' i 'B' és '0' la sortida és ((A.B) ̅) = (0 x 0) ̅ = '1' o 'HIGH'

Les condicions anteriors es simplifiquen a la taula de veritat.

Taula de veritat (dues entrades):

| A (entrada) | B (INPUT) | Y (sortida) |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Porta d'entrada 'NAND' de 3 entrades:

Il·lustració de la porta NAND de 3 entrades:

Les portes lògiques NAND poden tenir un nombre ‘n’ d’entrades, el que significa que pot tenir més de dues entrades

(Les portes NAND de la lògica tindran almenys dues entrades i sempre una sortida).

Per a una porta NAND de 3 entrades, l'equació booleana gira així: ((A.B.C) ̅) = Y, de manera similar per a 4 entrades i més.

Taula de la Veritatper a la porta NAND de 3 lògiques d'entrada:

| A (INPUT) | B (INPUT) | C (INPUT) | S (SORTIDA) |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Portes NAND de lògica d'entrada múltiple:

Les portes Logic NAND disponibles comercialment només estan disponibles en 2, 3 i 4 entrades. Si tenim més de 4 entrades, hem de posar en cascada les portes.

Per exemple, podem tenir quatre portes NAND lògiques d’entrada en cascada en dues portes NAND d’entrada de la següent manera:

Ara l’equació booleana del circuit anterior es converteix en Y = ((A.B.C.D) ̅)

Tot i això, totes les regles lògiques esmentades s'apliquen al circuit anterior.

Si utilitzeu només 3 entrades de la porta NAND de 4 entrades anteriors, podem connectar una resistència pull-up a qualsevol pin i ara es converteix en una porta NAND de 3 entrades.

Porta NAND lògica basada en dos transistors:

Ara ja sabem, com funciona una porta NAND lògica, construïm una porta NAND de 2 entrades usant-ne dues

Transistors NPN. Els CI lògics es construeixen gairebé de la mateixa manera.

Esquema de la porta NAND de dos transistors:

A la sortida “Y” podeu connectar un LED si la sortida és alta, el LED brillarà (terminal LED + Ve a “Y” amb una resistència de 330 ohm i negatiu a GND).

Quan apliquem un senyal alt a la base dels dos transistors, tots dos transistors s’encenen, el senyal de terra estarà disponible al col·lector de la T1, de manera que la sortida es convertirà en “BAIX”.

Si algun dels transistors està DESACTIVAT, és a dir, s’aplica un senyal “BAIX” a la base, no hi haurà cap senyal de terra disponible al col·lector de T1, però a causa de la resistència d’arrencada de 1 K, el senyal positiu estarà disponible a la sortida i la sortida gira 'ALT'.

Ara ja sabeu com construir la vostra porta lògica NAND.

Diverses portes lògiques que utilitzen la porta NAND:

La porta NAND també es coneix com a 'porta lògica universal' perquè podem fer qualsevol lògica booleana amb aquesta porta única. Aquest és un avantatge per fabricar circuits integrats amb funcions lògiques diferents i fabricar una sola porta és econòmic.

En els esquemes anteriors només es mostren 3 tipus de portes, però podem fer qualsevol lògica booleana.

Porta IC NAND quad 7400:

Si voleu comprar una porta NAND lògica del mercat, obtindreu la configuració DIP anterior.

Té 14 pins, el pin # 7 i el pin # 14 són GND i Vcc respectivament. Funciona a 5V.

Retard de propagació:

El retard de propagació és el temps que triga la sortida a canviar de BAIX a ALT i viceversa després de donar una entrada.

El retard de propagació de BAIX a ALT és de 22 nanosegons.

El retard de propagació d’ALTA a BAIXA és de 15 nanosegons.

Hi ha diversos altres IC de portes NAND disponibles:

- 74LS00 Quad 2 entrades

- 74LS10 Triple de 3 entrades

- 74LS20 Dual de 4 entrades

- 74LS30 Única entrada de 8

- CD4011 Quad 2 entrades

- CD4023 Triple de 3 entrades

- CD4012 Dual de 4 entrades

Com funciona la porta NOR

Aquí explorarem la lògica digital de la porta NOR. Farem una ullada a la definició bàsica, símbol, taula de veritat, porta NOR d’entrada múltiple, construirem una porta NOR d’entrada basada en transistors, diverses portes lògiques utilitzant només la porta NOR i, finalment, farem una visió general de la porta NOR IC 7402.

Què és Logic 'NOR' Gate?

És una porta electrònica, la sortida de la qual es converteix en 'HIGH' o '1' o 'true' o emet un 'senyal positiu' quan totes les entrades de les portes NOR són 'LOW' o '0' o 'false' o ' senyal negatiu ”.

Per exemple: Digueu una porta NOR amb el nombre 'n' d'entrades, si totes les entrades són 'BAIXES' la sortida es torna 'ALTA'. Fins i tot si una entrada és “HIGH” o “1” o “true” o “signal positiu”, la sortida es converteix en “LOW” o “0” o “false” o emet un “signal negatiu”.

Nota:

Els termes 'alt', '1', 'senyal positiu' i 'veritable' són essencialment el mateix (el senyal positiu és el senyal positiu de la bateria o de la font d'alimentació).

Els termes 'BAIX', '0', 'senyal negatiu' i 'fals' són essencialment el mateix (el senyal negatiu és el senyal negatiu de la bateria o de la font d'alimentació).

Il·lustració del símbol de porta NOR Logic:

Aquí la “A” i la “B” són les dues entrades i la sortida “Y”.

Aquest símbol és una porta 'OR' amb inversió 'o'.

Circuit equivalent de porta lògica “NOR”:

La porta lògica NOR és la combinació de porta lògica 'OR' i porta lògica 'NO'.

L’expressió booleana de la porta NOR lògica: la sortida ‘Y’ és una addició complementària de les dues entrades ‘A’ i ‘B’. Y = ((A + B) ̅)

L’addició booleana es denota amb (+) i la complementària (inversió) es representa amb una barra (-) sobre una lletra.

Si 'A' és '1' i 'B' és '1' la sortida és ((A + B) ̅) = (1+ 1) ̅ = '0' o 'BAIX'

Si 'A' és '0' i 'B' és '1', la sortida és ((A + B) ̅) = (0+ 1) ̅ = '0' o 'BAIX'

Si 'A' és '1' i 'B' és '0' la sortida és ((A + B) ̅) = (1+ 0) ̅ = '0' o 'BAIX'

Si 'A' és '0' i 'B' és '0', la sortida és ((A + B) ̅) = (0+ 0) ̅ = '1' o 'HIGH'

Les condicions anteriors es simplifiquen a la taula de veritat.

Taula de veritat (dues entrades):

| A (entrada) | B (INPUT) | Y (sortida) |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

Porta d'entrada 'NOR' de 3 entrades:

Il·lustració de la porta NOR de 3 entrades:

Les portes NOR lògiques poden tenir un nombre ‘n’ d’entrades, el que significa que pot tenir més de dues entrades (les portes NOR lògiques tindran almenys dues entrades i sempre una sortida).

Per a una porta NOR de 3 entrades, l'equació booleana gira així: ((A + B + C) ̅) = Y, de manera similar per a 4 entrades i més.

Taula de veritat per a la porta NOR de 3 lògiques d'entrada:

| A (INPUT) | B (INPUT) | C (INPUT) | S (SORTIDA) |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

Portes NOR de lògica d'entrada múltiple:

Les portes NOR Logic disponibles comercialment només estan disponibles en 2, 3 i 4 entrades. Si tenim més de 4 entrades, hem de posar en cascada les portes.

Per exemple, podem tenir quatre portes NOR de lògica d'entrada en cascada 5 dues portes NOR d'entrada de la següent manera:

Ara l'equació booleana del circuit anterior es converteix en Y = ((A + B + C + D) ̅)

Tot i això, totes les regles lògiques esmentades s'apliquen al circuit anterior.

Si utilitzeu només 3 entrades de la porta NOR de les 4 entrades anteriors, podem connectar una resistència desplegable a qualsevol dels pins i ara es converteix en una porta NOR de 3 entrades.

Porta NOR Lògica de dues entrades basada en transistors:

Ara ja sabem, com funciona una porta NOR lògica, construïm una porta NOR de 2 entrades mitjançant dos transistors NPN. Els CI lògics es construeixen gairebé de la mateixa manera.

Esquema de la porta NOR de dos transistors:

A la sortida “Y” podeu connectar un LED si la sortida és alta, el LED brillarà (terminal LED + Ve a “Y” amb una resistència de 330 ohm i negatiu a GND).

Quan apliquem el senyal 'HIGH' a la base dels dos transistors, tots dos transistors s'encenen i el senyal de terra estarà disponible al col·lector de T1 i T2, de manera que la sortida es convertirà en 'LOW'.

Si apliquem 'HIGH' a qualsevol transistor, el senyal negatiu estarà disponible a la sortida, fent que la sortida sigui 'BAIXA'.

Si apliquem senyal 'BAIX' a la base de dos transistors, tots dos s'apagaran, però a causa de la resistència de tracció, la sortida es convertirà en 'ALTA'.

Ara ja saps com construir la teva lògica NOR.

Diverses portes lògiques que utilitzen la porta NOR:

NOTA: NAND i NOR són les dues portes conegudes també com a portes universals.

La porta NOR també és una 'porta lògica universal' perquè podem fer qualsevol lògica booleana amb aquesta porta única. Aquest és un avantatge per fabricar circuits integrats amb funcions lògiques diferents i fabricar una sola porta és econòmic, això és el mateix per a la porta NAND.

Als esquemes anteriors només es mostren 3 tipus de portes, però podem fer qualsevol lògica booleana.

Quad NOR porta IC 7402:

Si voleu comprar una porta NOR lògica del mercat, obtindreu la configuració DIP anterior.

Té 14 pins, el pin # 7 i el pin # 14 són GND i Vcc respectivament. Funciona a 5V.

Retard de propagació:

El retard de propagació és el temps que triga la sortida a canviar de BAIX a ALT i viceversa després de donar una entrada.

El retard de propagació de BAIX a ALT és de 22 nanosegons.

El retard de propagació d’ALTA a BAIXA és de 15 nanosegons.

Hi ha diversos altres IC de porta NOR disponibles:

- 74LS02 Quad 2 entrades

- 74LS27 Triple 3 entrades

- 74LS260 Dual de 4 entrades

- CD4001 Quad 2 entrades

- CD4025 Triple 3 entrades

- CD4002 Doble entrada de 4

Lògica NO porta

En aquest post explorarem la porta lògica 'NO'. Coneixerem la seva definició bàsica, símbol, taula de veritat, equivalents de portes NAND i NOR, inversors Schmitt, oscil·lador de portes Schmitt, NO porta mitjançant transistor i, finalment, farem una ullada a l’inversor lògic NO de porta IC 7404.

Abans de començar a estudiar els detalls de la porta NO lògica, que també s'anomena inversor digital, no s'ha de confondre amb els 'inversors de potència' que s'utilitzen en fonts d'alimentació solars o de seguretat a casa o a l'oficina.

Què és Logic Gate 'NOT'?

És una porta lògica d'entrada i sortida única la sortida del qual és complementària a l'entrada.

La definició anterior afirma que si l'entrada és 'ALTA' o '1' o 'veritable' o 'senyal positiu' la sortida serà 'BAIXA' o '0' o 'falsa' o 'senyal negativa'.

Si l'entrada és 'BAIX' o '0' o 'fals' o 'senyal negatiu' la sortida s'invertirà a 'ALTA' o '1' o 'veritable' o 'senyal positiu'

Nota:

Els termes 'alt', '1', 'senyal positiu' i 'veritable' són essencialment el mateix (el senyal positiu és el senyal positiu de la bateria o de la font d'alimentació).

Els termes 'BAIX', '0', 'senyal negatiu' i 'fals' són essencialment el mateix (el senyal negatiu és el senyal negatiu de la bateria o de la font d'alimentació).

Il·lustració de Logic NOT Gate:

Suposem que 'A' és l'entrada i 'Y' és la sortida, l'equació booleana de la porta NO lògica és: Ā = Y.

L'equació indica que la sortida és la inversió de l'entrada.

Taula de veritat per a la lògica NO porta:

| A (ENTRADA) | I (SORTIDA) |

| 0 | 1 |

| 1 | 0 |

Les portes no sempre tenen una única entrada (i sempre tenen una única sortida), es classifica com a dispositius de presa de decisions. El símbol “o” a la punta del triangle representa la complementació o la inversió.

Aquest símbol 'o' no només es limita a la porta lògica 'NO', sinó que també pot ser utilitzat per qualsevol porta lògica o qualsevol circuit digital. Si la 'o' és a l'entrada, això indica que l'entrada és activa-baixa.

Actiu-Baix: la sortida es torna activa (activant un transistor, un LED o un relé, etc.) quan es dóna l'entrada “BAIX”.

Equivalent de portes NAND i NOR:

La porta 'NO' es pot construir utilitzant portes lògiques 'NAND' i lògiques 'NOR' unint tots els pins d'entrada, això s'aplica a les portes amb pins d'entrada de 3, 4 i superiors.

Porta lògica basada en transistors 'NO':

La lògica 'NO' es pot construir mitjançant un transistor NPN i una resistència 1K. Si apliquem senyal 'HIGH' a la base del transistor, la terra es connecta al col·lector del transistor, de manera que la sortida es torna 'BAIXA'.

Si apliquem el senyal 'BAIX' a la base del transistor, el transistor romandrà apagat i no es connectarà a terra, però la sortida es tirarà 'ALTA' mitjançant la connexió de la resistència de tracció a Vcc. Així aconseguim que es pot fer una porta lògica 'NO' mitjançant transistor.

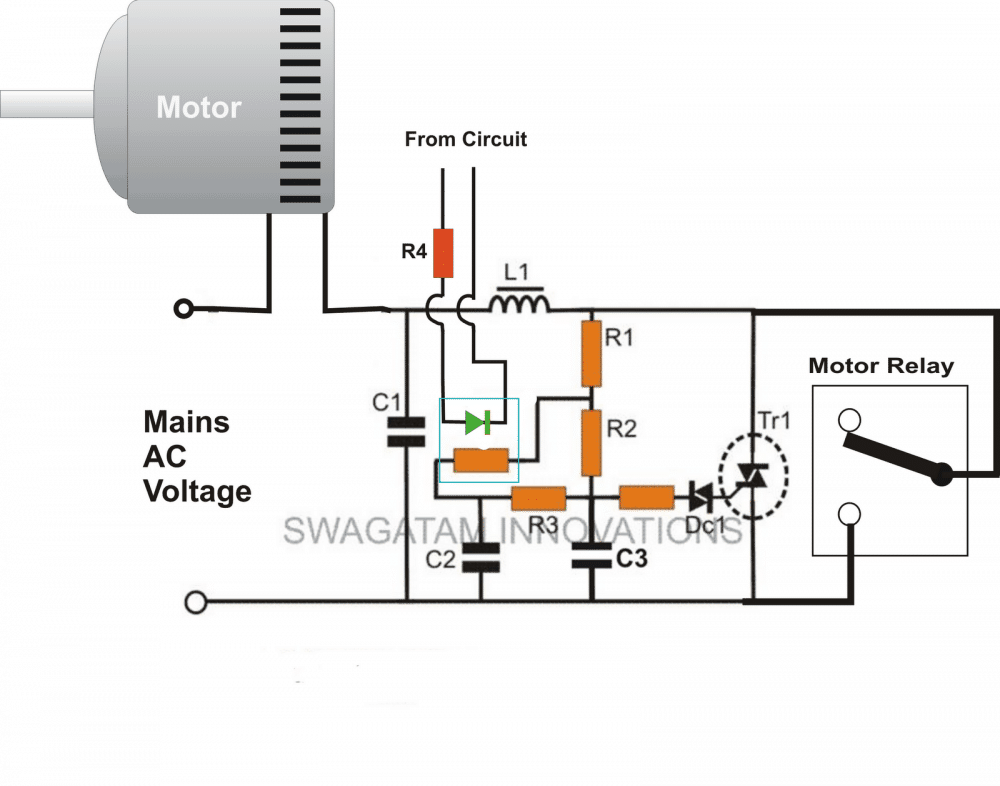

Inversors Schmitt:

Explorarem aquest concepte amb un carregador de bateria automàtic per explicar l’ús i el funcionament dels inversors Schmitt. Posem l’exemple del procediment de càrrega de la bateria de li-ion.

La bateria de 3,7 V li-ion es carrega quan la bateria arriba a 3 V a 3,2 V, la tensió de la bateria augmenta gradualment mentre es carrega i la bateria s’ha de tallar a 4,2 V. Després de carregar-se, la tensió del circuit obert de la bateria cau al voltant de 4,0 V .

Un sensor de tensió mesura el límit de tall i provoca que el relé deixi de carregar-se. Però quan la tensió baixa per sota de 4,2 V, el carregador detecta que no està carregat i comença a carregar-se fins a 4,2 V i es talla, de nou, el voltatge de la bateria cau a 4,0 V i torna a començar la càrrega i aquesta bogeria fa cicles una i altra vegada.

Això matarà la bateria ràpidament, per superar aquest problema necessitem un nivell de llindar inferior o “LTV” perquè la bateria no es comenci a carregar fins que la bateria caigui de 3 V a 3,2 V. La tensió del llindar superior o “UTV” és 4.2V en aquest exemple.

Es fa un inversor Schmitt per canviar el seu estat de sortida quan la tensió creua la tensió del llindar superior i es manté fins que l’entrada arriba al voltatge del llindar inferior.

De la mateixa manera, una vegada que l’entrada creua la tensió llindar inferior, la sortida es manté fins que l’entrada arriba al voltatge llindar superior.

No canviarà el seu estat entre LTV i UTV.

Ara, a causa d'això, l'encesa / apagada serà molt més suau i s'eliminaran les oscil·lacions no desitjades i el circuit serà més resistent al soroll elèctric.

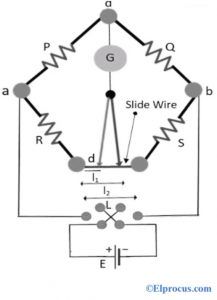

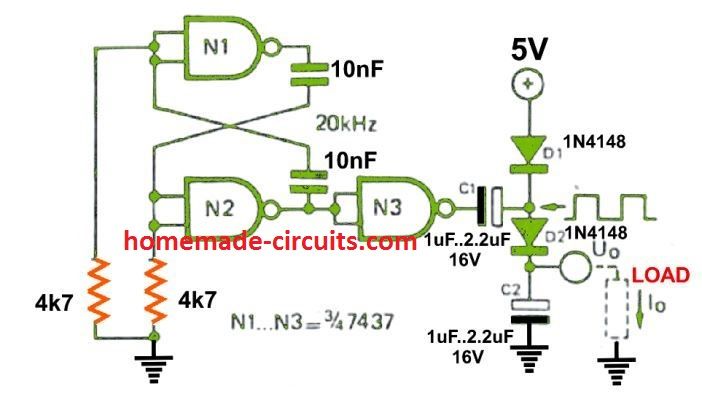

Oscil·lador Schmitt NOT Gate:

El circuit anterior és un oscil·lador que produeix ona quadrada al 33% de cicle de treball. Inicialment, el condensador està descarregat i el senyal de terra estarà disponible a l'entrada de la porta NOT.

La sortida es torna positiva i carrega el condensador a través de la resistència “R”, el condensador es carrega fins a la tensió llindar superior de l’inversor i canvia l’estat, la sortida gira el senyal negatiu i el condensador comença a descarregar-se a través de la resistència “R” fins que la tensió del condensador arriba el nivell de llindar inferior i canvia l'estat, la sortida es torna positiva i carrega el condensador.

Aquest cicle es repeteix mentre es dóna la font d'alimentació al circuit.

Es pot calcular la freqüència de l’oscil·lador anterior: F = 680 / RC

On, F és freqüència.

R és la resistència en ohms.

C és la capacitat de farad.

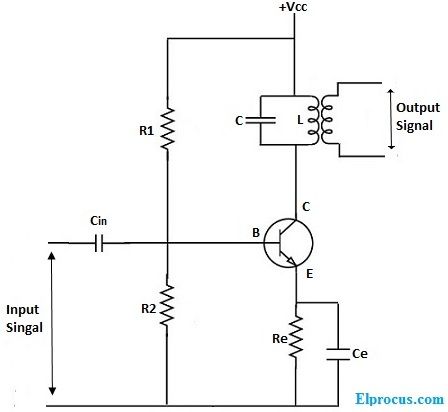

Convertidor d'ona quadrada:

El circuit anterior convertirà el senyal d'ona sinusoïdal en ona quadrada, en realitat pot convertir qualsevol ona analògica en ona quadrada.

Les dues resistències R1 i R2 funcionen com a divisor de voltatge, s’utilitza per obtenir un punt de polarització i el condensador bloqueja qualsevol senyal de CC.

Si el senyal d'entrada supera el nivell de llindar superior o per sota del nivell de llindar inferior, la sortida gira

BAIX o ALT segons el senyal, produeix ona quadrada.

Inversor de porta IC 7404 NOT:

L'IC 7404 és un dels IC lògics NO de porta més utilitzats. Té 14 pins, el pin # 7 està mòlt i el pin # 14 és Vcc. La tensió de funcionament és de 4,5V a 5V.

Retard de propagació:

El retard de propagació és el temps que triga la porta a processar la sortida després de donar una entrada.

En lògica, la porta 'NO' triga uns 22 nano segons a canviar el seu estat d'Alta a Baixa i viceversa.

Hi ha diverses altres lògiques 'NO porta ICs:

• 74LS04 Hex Inverting NOT Gate

• 74LS14 Hex Schmitt Inverting NOT Gate

• Controladors d'inversió hexagonals 74LS1004

• CD4009 Hex Inverting NOT Gate

• CD4069 Hex Inverting NOT Gate

Com funciona la porta OR

Ara explorem la lògica digital O les portes. Farem una ullada a la definició bàsica, símbol, taula de veritat, porta d’entrada múltiple, construirem una porta d’entrada basada en transistor de 2 entrades i, finalment, farem una visió general de la porta d’or IC 7432.

Què és Logic 'OR' Gate?

És una porta electrònica, la sortida de la qual es converteix en 'BAIX' o '0' o 'fals' o emet un 'senyal negatiu' quan totes les entrades de les portes OR són 'BAIX' o '0' o 'fals' o ' senyal negatiu ”.

Per exemple: Digueu una porta OR amb el nombre 'n' d'entrades, si totes les entrades són 'BAIXES', la sortida es convertirà en 'BAIXES'. Fins i tot si una entrada és “HIGH” o “1” o “true” o “signal positiu”, la sortida es converteix en “HIGH” o “1” o “true” o emet un “senyal positiu”.

Nota:

Els termes 'alt', '1', 'senyal positiu' i 'veritable' són essencialment el mateix (el senyal positiu és el senyal positiu de la bateria o de la font d'alimentació).

Els termes 'BAIX', '0', 'senyal negatiu' i 'fals' són essencialment el mateix (el senyal negatiu és el senyal negatiu de la bateria o de la font d'alimentació).

Il·lustració del símbol Logic OR gate:

Aquí la “A” i la “B” són les dues entrades i la sortida “Y”.

L’expressió booleana de la porta lògica O: la sortida ‘Y’ és l’addició de les dues entrades ‘A’ i ‘B’, (A + B) = Y.

L'addició booleana es denota amb (+)

Si 'A' és '1' i 'B' és '1' la sortida és (A + B) = 1 + 1 = '1' o 'alta'

Si 'A' és '0' i 'B' és '1' la sortida és (A + B) = 0 + 1 = '1' o 'alta'

Si 'A' és '1' i 'B' és '0' la sortida és (A + B) = 1 + 0 = '1' o 'alta'

Si 'A' és '0' i 'B' és '0' la sortida és (A + B) = 0 + 0 = '0' o 'Baixa'

Les condicions anteriors es simplifiquen a la taula de veritat.

Taula de veritat (dues entrades):

| A (entrada) | B (INPUT) | Y (sortida) |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Porta d'entrada 'O' de 3 entrades:

Il·lustració de 3 entrades O porta:

Les portes OR lògiques poden tenir un nombre ‘n’ d’entrada, el que significa que pot tenir més de dues entrades (les portes OR lògiques tindran com a mínim dues entrades i sempre una sortida).

Per a una porta lògica d'entrada de 3 O l'equació booleana gira així: (A + B + C) = Y, de manera similar per a 4 entrades i superiors.

Taula de veritat per a una lògica d'entrada O porta:

| A (INPUT) | B (INPUT) | C (INPUT) | S (SORTIDA) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Lògica d'entrada múltiple O portes:

Les portes lògiques o lògiques disponibles comercialment només estan disponibles en 2, 3 i 4 entrades. Si tenim més de 4 entrades, hem de posar en cascada les portes.

Podem tenir sis portes lògiques d’entrada O en cascada de les dues portes OR d’entrada de la següent manera:

Ara l'equació booleana del circuit anterior es converteix en Y = (A + B) + (C + D) + (E + F)

Tot i això, totes les regles lògiques esmentades s'apliquen al circuit anterior.

Si utilitzeu només 5 entrades de les 6 portes OR anteriors, podem connectar una resistència desplegable a qualsevol pin i ara es converteix en una porta OR 5 entrades.

Porta lògica o entrada basada en dos transistors:

Ara sabem, com funciona una porta lògica OR, construïm una porta OR de 2 entrades mitjançant dos transistors NPN. Els CI lògics es construeixen gairebé de la mateixa manera.

Esquema de dos transistors O porta:

A la sortida “Y” podeu connectar un LED si la sortida és alta, el LED brillarà (terminal LED + Ve a “Y” amb una resistència de 330 ohm i negatiu a GND).

Quan apliquem el senyal BAIX a la base dels dos transistors, tots dos transistors s’APAGEN, el senyal de terra estarà disponible a l’emissor del T2 / T1 mitjançant una resistència desplegable d’1 k, de manera que la sortida es torna BAIXA.

Si algun transistor està engegat, hi haurà tensió positiva a l’emissor de T2 / T1, de manera que la sortida serà ALTA.

Ara ja saps com construir una lògica O una porta pròpia.

IC 7432 de quatre portes O:

Si voleu comprar una porta lògica O del mercat, obtindreu la configuració anterior.

Té 14 pins, el pin # 7 i el pin # 14 són GND i Vcc respectivament. Funciona a 5V.

Retard de propagació:

El retard de propagació és el temps que triga la sortida a canviar de BAIX a ALT i viceversa.

El retard de propagació de BAIX a ALT és de 7,4 nanosegons a 25 graus centígrads.

El retard de propagació d’ALTA a BAIXA és de 7,7 nanosegons a 25 graus centígrads.

• 74LS32 Quad 2 entrades

• CD4071 Quad 2 entrades

• CD4075 Triple 3 entrades

• CD4072 Dual de 4 entrades

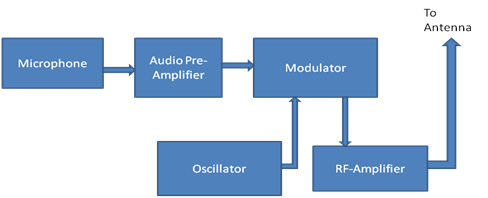

Logic Exclusive –OR Gate

En aquest post explorarem la porta lògica XOR o la porta exclusiva-OR. Farem una ullada a la definició bàsica, símbol, taula de veritat, circuit equivalent a XOR, realització de XOR mitjançant portes lògiques NAND i, finalment, farem una visió general de la porta Ex-OR IC 7486 d’entrada quad 2.

A les entrades anteriors, vam aprendre sobre tres portes lògiques fonamentals “I”, “O” i “NO”. També vam aprendre que, utilitzant aquestes tres portes fonamentals, podem construir dues noves portes lògiques 'NAND' i 'NOR'.

Hi ha dues portes lògiques més, tot i que aquestes dues no són portes bàsiques, sinó que es construeixen mitjançant la combinació de les altres portes lògiques i la seva equació booleana és tan vital i molt útil que es considera com a portes lògiques diferents.

Aquestes dues portes lògiques són 'Exclusive OR' gate i 'Exclusive NOR'. En aquest post, només explorarem la lògica exclusiva de la porta OR.

Què és la porta 'OR exclusiva'?

És una porta electrònica, la sortida de la qual es converteix en 'alta' o '1' o 'vertadera' o emet un 'senyal positiu' quan les dues entrades lògiques són diferents entre si (això només s'aplica a dues entrades Ex -O porta).

Per exemple: Digueu una porta OR exclusiva amb 'dues' entrades, si un dels pins d'entrada A és 'HIGH' i el pin d'entrada B és 'LOW', la sortida es torna 'HIGH' o '1' o 'true' o “Senyal positiu”.

Si les dues entrades tenen el mateix nivell lògic, és a dir, ambdós pins “HIGH” o ambdós pins “LOW” la sortida es convertirà en “LOW” o “0” o “false” o “signal negatiu”.

Nota:

Els termes 'alt', '1', 'senyal positiu' i 'veritable' són essencialment el mateix (el senyal positiu és el senyal positiu de la bateria o de la font d'alimentació).

Els termes 'BAIX', '0', 'senyal negatiu' i 'fals' són essencialment el mateix (el senyal negatiu és el senyal negatiu de la bateria o de la font d'alimentació).

Il·lustració de Logic Exclusive OR gate:

Aquí la “A” i la “B” són les dues entrades i la sortida “Y”.

L'expressió booleana de la porta lògica Ex-OR: Y = (A.) ̅B + A.B ̅

Si 'A' és '1' i 'B' és '1' la sortida és (A ̅.B + A.B ̅) = 0 x 1 + 1 x 0 = '1' o 'BAIX'

Si 'A' és '0' i 'B' és '1', la sortida és (A ̅.B + A.B ̅) = 1 x 1 + 0 x 0 = '1' o 'HIGH'

Si 'A' és '1' i 'B' és '0' la sortida és (A ̅.B + A.B ̅) = 0 x 0 + 1 x 1 = '1' o 'HIGH'

Si 'A' és '0' i 'B' és '0' la sortida és (A ̅.B + A.B ̅) = 1 x 0 + 0 x 1 = '0' o 'Baix'

Les condicions anteriors es simplifiquen a la taula de veritat.

Taula de veritat (dues entrades):

| A (entrada) | B (INPUT) | Y (sortida) |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

A les dues portes Ex-OR de la lògica d’entrada anterior, si les dues entrades són diferents, és a dir, “1” i “0” la sortida es converteix en “HIGH”. Però amb 3 o més lògiques d’entrada Ex-OR o, en general, la sortida de Ex-OR es converteix en “HIGH” només quan s’aplica el número imparell de la lògica “HIGH” a la porta.

Per exemple: Si tenim 3 portes Ex-OR d’entrada, si apliquem la lògica “HIGH” a una sola entrada (nombre senar de lògica “1”) la sortida es convertirà en “HIGH”. Si apliquem la lògica “HIGH” a dues entrades (aquest és el nombre parell de la lògica “1”), la sortida es convertirà en “LOW” i així successivament.

Porta d'entrada exclusiva de 3 entrades:

Il·lustració de la porta EX-OR de 3 entrades:

Taula de veritat per a la porta EX-OR de la lògica d'entrada de 3:

| A (INPUT) | B (INPUT) | C (INPUT) | S (SORTIDA) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

Per a la porta Ex-OR de 3 entrades, l'equació booleana es converteix en: A (BC) ̅ + A ̅BC ̅ + (AB) ̅C + ABC

Com hem descrit abans, la porta lògica 'Ex-OR' no és una porta lògica fonamental, sinó la combinació de diferents portes lògiques. La porta Ex-OR es pot realitzar utilitzant la porta lògica “OR”, la porta lògica “AND” i la porta lògica “NAND” de la següent manera:

Circuit equivalent per a la porta 'Exclusive OR':

El disseny anterior té un gran inconvenient, necessitem 3 portes lògiques diferents per fer una porta Ex-OR. Però podem superar aquest problema implementant una porta Ex-OR amb només portes NAND lògiques, això també és econòmic fabricar.

Porta O exclusiva amb porta NAND:

Les portes OR exclusives s’utilitzen per realitzar tasques informàtiques complicades, com ara operacions aritmètiques, sumadors complets, mitges sumadores, també poden oferir funcionalitats.

IC lògica exclusiva O porta IC 7486:

Si voleu comprar una porta lògica Ex-OR del mercat, obtindreu la configuració DIP anterior.

Té 14 pins, el pin # 7 i el pin # 14 són GND i Vcc respectivament. Funciona a 5V.

Retard de propagació:

El retard de propagació és el temps que es triga a canviar la sortida de BAIX a ALT i viceversa després de donar entrada.

El retard de propagació de BAIX a ALT és de 23 nanosegons.

El retard de propagació d’ALTA a BAIXA és de 17 nanosegons.

ICs de porta 'EX-OR' disponibles habitualment:

- 74LS86 Quad 2 entrades

- CD4030 Quad 2 entrades

Espero que l'explicació detallada anterior us hagi ajudat a entendre què són les portes lògiques i com funcionen les portes lògiques, si encara teniu cap pregunta? Si us plau, expressa a la secció de comentaris, és possible que obtinguis una resposta ràpida

Anterior: Circuit de prova de fuites de condensadors: trobeu condensadors de fuites ràpidament Següent: Memòria intermèdia digital: funcionament, definició, taula de veritat, doble inversió, ventilació