El bucle bloquejat de fase és un dels blocs bàsics dels sistemes electrònics moderns. S’utilitza generalment en multimèdia, comunicació i en moltes altres aplicacions. Hi ha dos tipus diferents de PLL: lineals i no lineals. El no lineal és difícil i complicat de dissenyar al món real, però la teoria del control lineal està ben modelada en els PLL analògics. El PLL ha demostrat que un model lineal és suficient per a la majoria de les aplicacions electròniques.

Què és un bucle de bloqueig de fase?

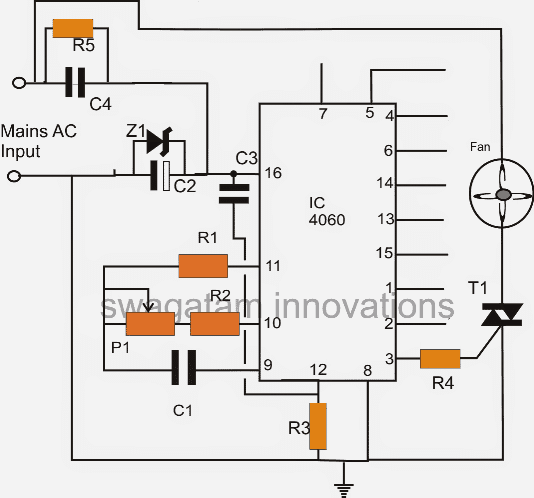

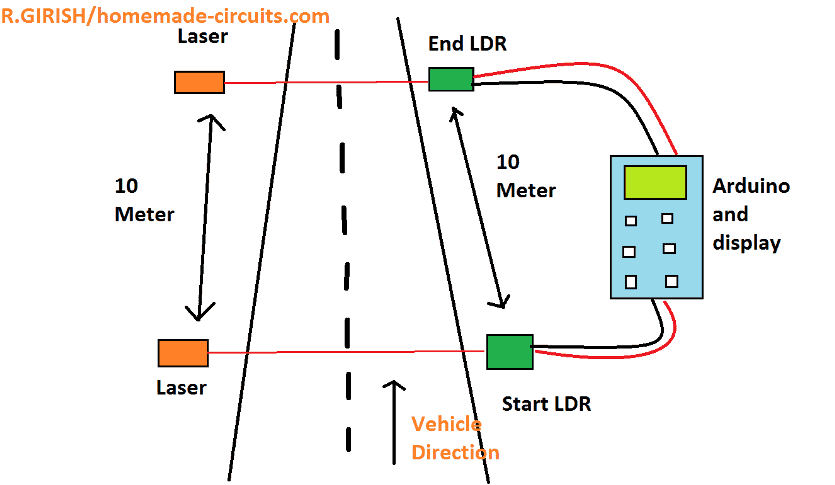

Un bucle bloquejat de fase consisteix en un detector de fase i un oscil·lador controlat per tensió. La sortida del detector de fase és l’entrada de l’oscil·lador controlat per tensió (VCO) i la sortida del VCO està connectada a una de les entrades d’un detector de fase que es mostra a continuació al diagrama de blocs bàsic. Quan aquests dos dispositius s’alimenten mútuament es forma el bucle.

DIAGRAMA BÀSIC DE LAÇA BLOCADA EN FASE

Diagrama de blocs i principi de funcionament de PLL

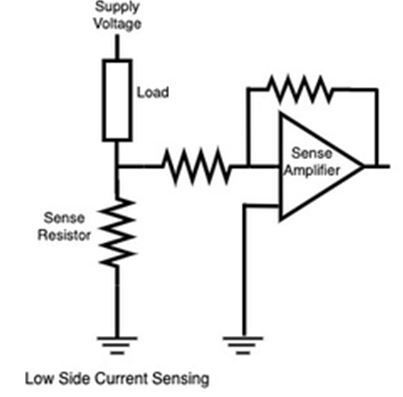

El bucle bloquejat de fase consisteix en un detector de fase, a oscil·lador controlat per tensió i, entre ells, es fixa un filtre de pas baix. El detector de fase concedeix el senyal d’entrada ‘Vi’ amb una freqüència d’entrada ‘Fi’. Bàsicament el detector de fase és un comparador que compara la freqüència d'entrada fi a través de la freqüència de retroalimentació fo. La sortida del detector de fase és (fi + fo), que és un voltatge continu. El detector fora de fase, és a dir, s’introdueix la tensió CC al filtre de pas baix (LPF), elimina el soroll d’alta freqüència i produeix un nivell continu de CC, és a dir, Fi-Fo. El Vf també és una característica dinàmica del PLL.

Diagrama de blocs PLL

La sortida del filtre de pas baix, és a dir, el nivell de CC es transmet al VCO. El senyal d’entrada és directament proporcional a la freqüència de sortida del VCO (fo). Les freqüències d'entrada i sortida es comparen i s'ajusten a través del bucle de retroalimentació fins que la freqüència de sortida sigui igual a la freqüència d'entrada. Per tant, el PLL funciona com el funcionament lliure, la captura i el bloqueig de fase.

Quan no s’aplica cap tensió d’entrada, es diu que és una etapa de funcionament lliure. Tan aviat com la freqüència d'entrada aplicada al COV canvia i produeix una freqüència de sortida per a la comparació, s'anomena etapa de captura. La figura següent mostra el diagrama de blocs del PLL.

Detector de bucle bloquejat de fase

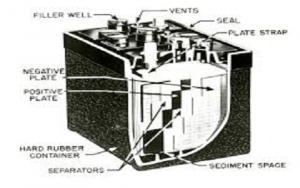

El detector de bucle bloquejat de fase compara la freqüència d'entrada i la freqüència de sortida del VCO per produir una tensió de CC que és directament proporcional a la distinció de fase de les dues freqüències. Els senyals analògics i digitals s’utilitzen en el bucle de bloqueig de fase. La majoria dels PLL monolítics circuits integrats utilitzeu un detector de fase analògic i la majoria dels detectors de fase són del tipus digital. Un circuit de mescla de doble equilibri s’utilitza habitualment en detectors de fase analògics. A continuació es detallen alguns detectors de fase comuns:

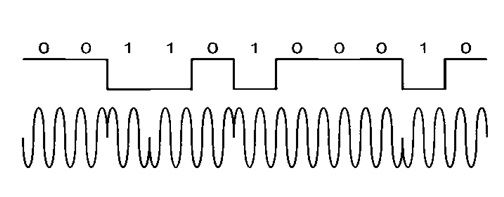

Detector de fase O exclusiu

Un detector de fase O exclusiu és el tipus CMOS IC 4070. Les freqüències d’entrada i sortida s’apliquen al detector de fase EX OR. Per obtenir una sortida alta, almenys una entrada ha de ser baixa i les altres condicions de sortida són baixes, com es mostra a la taula de veritat següent. Considerem la forma d'ona, les freqüències d'entrada i sortida, és a dir, fi i fo tenen una diferència de fase de 0 graus. Llavors, el voltatge de sortida de CC del comparador serà una funció de la diferència de fase entre les dues entrades.

| ser | fo | Vdc |

baix | baix | baix |

baix | alt | alt |

alt | baix | alt |

Alt | Alt | baix |

Les funcions de la diferència de fase entre el fi i el fo són les que es mostren a la gràfica del voltatge de sortida de CC. Si el detector de fase és de 180 graus, el voltatge de sortida és màxim. Si les freqüències d'entrada i sortida són d'ona quadrada, s'utilitzaran aquest tipus de detectors de fase.

Detector de fase O exclusiu

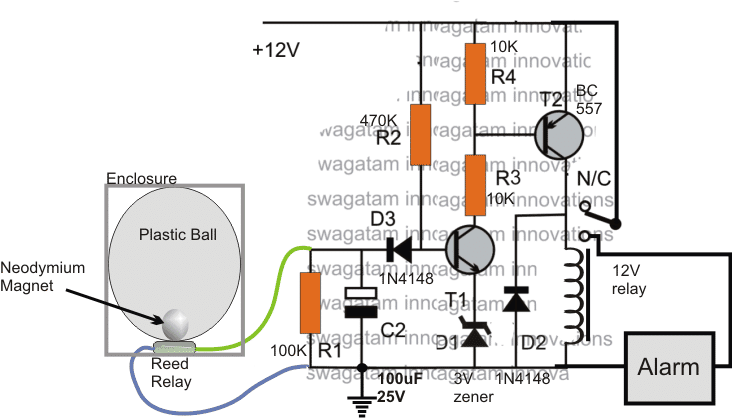

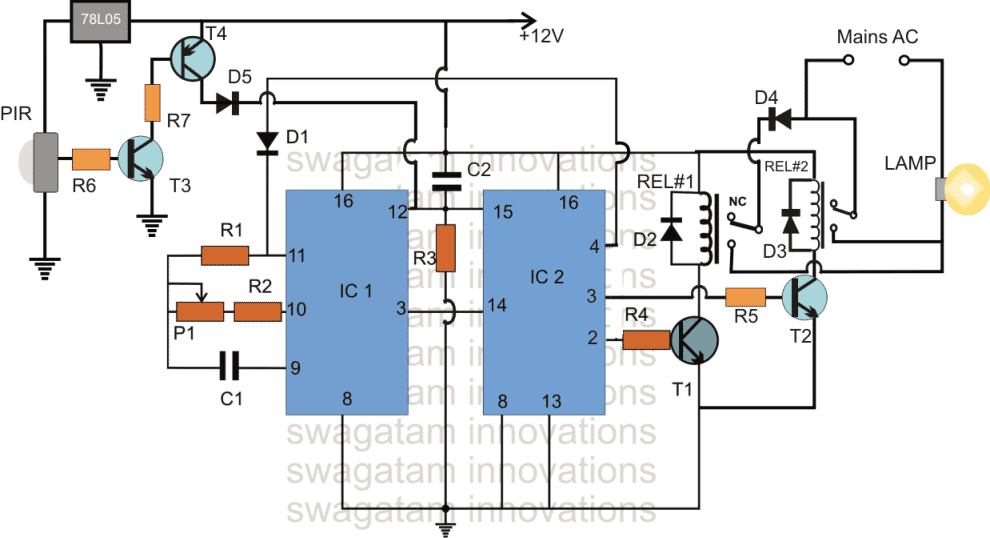

Detector de fase del disparador de vora

Un detector de fase de disparador de vora s’utilitza quan les freqüències d’entrada i sortida es troben en forma d’ona de pols, que és inferior al 50% del cicle de treball. El xanclet R-S s’utilitza per als detectors de fase, que es mostra a la figura següent. Des de R-S xancletes , les dues portes NOR estan acoblades creuadament. La sortida del detector de fase pot canviar el seu estat lògic activant el xanclet R-S. La vora positiva de les freqüències d’entrada i sortida pot canviar la sortida del detector de fase.

Detector de fase del disparador de vora

Detector de fases monolítiques

Un detector de fase monolític és de tipus CMOS, és a dir, IC 4044. Està altament compensat per la sensibilitat harmònica i s’abandonen els problemes del cicle de treball ja que el circuit només pot respondre a la transició del senyal d’entrada. En aplicacions crítiques, és el detector de fase amb més febre. Les variacions independents de l'amplitud estan lliures de l'error de fase, la tensió d'error de sortida i el cicle de treball de les formes d'ona d'entrada.

Aplicacions del bucle bloquejat per fase

- Xarxes de demodulació de FM per a operacions de FM

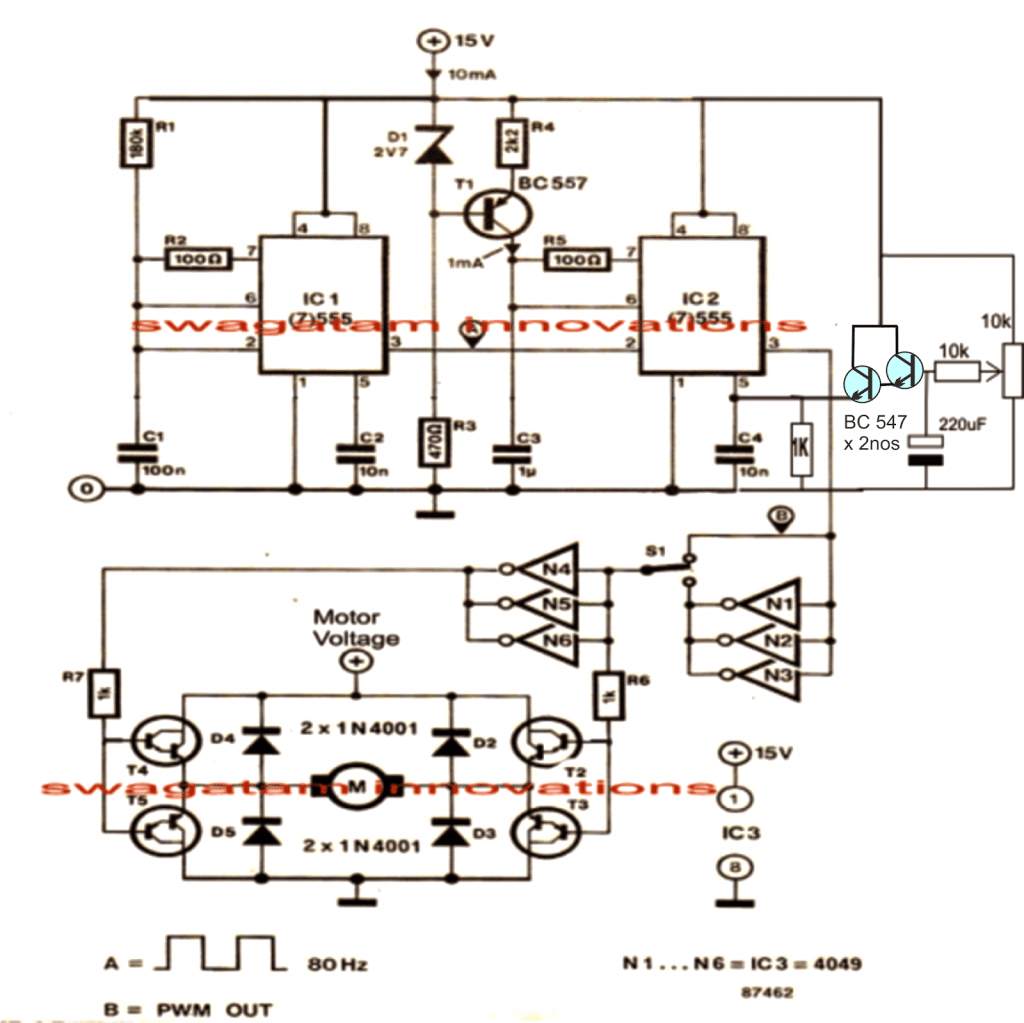

- S'utilitza a controls de velocitat del motor i filtres de seguiment.

- S'utilitza en decodificacions de desplaçament de freqüència per a les freqüències de portadors de demodulació.

- S'utilitza a temps per convertir convertidors digitals.

- S'utilitza per reduir la fluctuació, supressió d'inclinacions, recuperació del rellotge.

Es tracta del principi de funcionament i funcionament del bucle bloquejat de fase i de les seves aplicacions. Esperem que la informació que es proporciona a l'article us sigui útil per saber alguna cosa sobre el projecte i entendre'l. A més, si teniu cap pregunta sobre aquest article i sobre projectes elèctrics i electrònics podeu fer comentaris a la secció següent. Aquí teniu una pregunta, quina és la millor manera de simular l'estabilitat del PLL?

Crèdits fotogràfics:

- Diagrama de blocs de PLL avui en dia

- Detector de fase O exclusiu sanfunderia

- Detector de fase del disparador de vora APRENENT-ELECTRONNICA