En general, el restador complet és un dels més utilitzats i circuits lògics combinacionals essencials . És un dispositiu electrònic bàsic, utilitzat per a la resta de dos nombres binaris. A l'article anterior, ja hem donat la teoria bàsica de mig sumador i un sumador complet que utilitza els dígits binaris per al càlcul. De la mateixa manera, el restador complet utilitza dígits binaris com 0,1 per a la resta. El circuit d'això es pot construir amb portes lògiques com OR, Ex-OR, NAND gate. Les entrades d’aquest subtractor són A, B, Bin i les sortides són D, Bout.

Aquest article dóna una idea de teoria de subtractors complets que inclou premisses com el que és un subtractor, disseny amb portes lògiques, taula de veritat, etc. Aquest article és útil per a estudiants d’enginyeria que poden examinar aquests temes al laboratori pràctic HDL.

Què és un subtractor?

La resta de dígits binaris es pot fer amb l'ajut del circuit de la resta. Aquest és un tipus de circuit lògic combinacional, utilitzat per realitzar la resta de dos dígits binaris com 0s i 1s. La resta de dígits binaris de 0 a 0 o de 0 a 1 no altera el resultat, la resta de 1 a 1 resultarà com a 0, però la resta de 1 a 0 necessita un préstec.

Per exemple, el circuit de substracció de dos bits inclou dues entrades com A & B, mentre que les sortides són diferencials i manlleven. Aquest circuit es pot construir amb sumadors juntament amb inversors que es troben entre totes les dades d’entrada, així com les entrades de préstec (Bin) de la fase anterior de FA.

Els restants es classifiquen en dos tipus, com ara el mitjà restador i el restador complet. Aquí estem discutint el subtractor complet.

Què és un subtractor complet?

És un dispositiu electrònic o circuit lògic que realitza la resta de dos dígits binaris. És un circuit lògic combinacional utilitzat en electrònica digital. Hi ha molts circuits combinatius disponibles a tecnologia de circuits integrats és a dir, sumadors, codificadors, descodificadors i multiplexors. En aquest article, analitzarem la seva construcció mitjançant mitjà substractor i també els termes com a taula de veritat.

Subtractor complet

El disseny d’això es pot fer mitjançant dos mitjans restadors, que impliquen tres entrades com minuend, subtrahend i borrow, el bit de préstec entre les entrades s’obté de la resta de dos dígits binaris i es resta del següent parell d’ordre superior de bits, sortides com a diferència i préstec.

El diagrama de blocs de restador complet es mostra a continuació. L’inconvenient més important del mig restador és que no podem fer un bit de préstec en aquest subtractor. Mentre que en el seu disseny, en realitat podem fer un bit Borrow al circuit i restar amb els dos i / ps restants. Aquí A és minuend, B és subtrahend i Bin es manlleva. Les sortides són Difference (Diff) i Bout (Borrow out). El circuit de restador complet es pot obtenir utilitzant dos mitges restants amb una porta OR addicional.

Diagrama de circuits complet de subtractors amb portes lògiques

El diagrama de circuits del subtractor complet mitjançant una porta bàsica s es mostra al següent diagrama de blocs. Aquest circuit es pot fer amb dos circuits de mitja resta.

En el circuit inicial de mitja substracció, les entrades binàries són A i B. Com hem comentat a l’article anterior de mitja substracció, generarà dues sortides, a saber, diferència (Diff) i Borrow.

Subtractor complet amb Logic Gates

La diferència o / p del substracte esquerre es dóna als circuits del mig restador esquerre. A més, es proporciona una sortida de diferència a l’entrada de la meitat del circuit Subtractor. Vam oferir el préstec en bit a l'altre i / p del següent circuit mitjà restador . Una vegada més donarà tant a Diff com a Borrow. La sortida final d’aquest subtractor és Diff-output.

D'altra banda, el préstec dels dos circuits de la resta del subtractor està connectat a la porta lògica OR. Més tard que donar una lògica OR per a dos bits de sortida del subtractor, adquirim el préstec final del subtractor. L'últim Borrow out per significar el MSB (una mica més significatiu).

Si observem el circuit intern d’aquest, podem veure dos mitjans restadors amb porta NAND i porta XOR amb una porta OR addicional.

Taula de veritat de subtractor complet

Això circuit de resta executa una resta entre dos bits, que té 3 entrades (A, B i Bin) i dues sortides (D i Bout). Aquí les entrades indiquen minuend, subtrahend i prestat anterior, mentre que les dues sortides es denoten com a prestat o / p i diferència. La imatge següent mostra la taula de veritat del subtractor complet.

Entrades | Sortides | |||

Minuend (A) | Subtrahend (B) | Prestar (paperera) | Diferència (D) | Préstec (Bout) |

0 | 0 | 0 | 0 | 0 |

0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

Mapa K

La simplificació del K-mapa de restador complet a continuació es mostra la diferència i el préstec anteriors.

A continuació s’esmenten les equacions de la diferència i Bin.

L’expressió de Difference és:

D = A’B’Bin + AB’Bin ’+ A’BBin’ + ABBin

L’expressió de Borrow és:

Bout = A’Bin + A’B + BBin

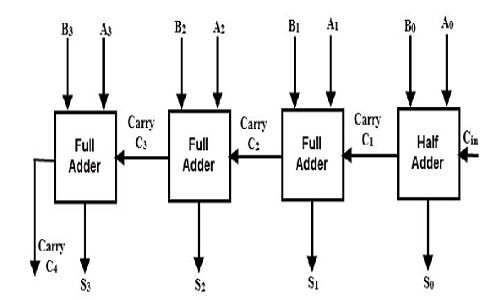

Cascada del circuit complet de substracció

Anteriorment, hem discutit una visió general d'aquest tema com la construcció, un diagrama de circuits amb portes lògiques. Però si volem restar dos nombres d'1 bit, en cas contrari, aquest circuit de substracció és molt útil per obtenir en cascada nombres de bits únics i també resta més de dos nombres binaris. En aquests casos, s'utilitza un circuit en cascada de sumador complet amb l'ajuda de la porta lògica NOT. La conversió del circuit de sumador complet a subtractor complet es pot fer mitjançant la tècnica del complement de 2.

En general, invertiu les entrades de subtrahend per al sumador complet mitjançant la porta NOT d'una altra manera un inversor. En afegir aquest minuend (entrada no inversa) i subtrahend (entrada invertida), la LSB (entrada de transport) del circuit FA és 1, el que significa que la lògica és alta si restem dos dígits binaris mitjançant la tècnica del complement de 2. La sortida de la FA és el bit Diff i, si invertim la realització, podem obtenir el MSB en cas contrari, el bit Borrow. En realitat, podem dissenyar el circuit de manera que es pugui observar la sortida.

Codi Verilog

Per a la part de codificació, primer, hem de comprovar la forma estructural de modelar el diagrama del circuit lògic. El diagrama lògic d’això es pot construir utilitzant una porta AND, circuits de mitja resta, i la combinació de portes lògiques com portes XOR, AND, OR, NOT. Com en el modelatge estructural, expliquem diversos mòduls per a cada disposició elemental bàsica. Al codi següent, es poden definir diferents mòduls per a cada porta.

Aquest mòdul és per a la porta OR.

ENTRADA: a0, b0

SORTIDA: c0

Per últim, unirem aquests mòduls precisos de porta en un únic mòdul. Per a això, aquí fem servir la instanciació del mòdul. Ara aquesta instanciació es pot utilitzar una vegada que vulguem replicar un mòdul o una funció exacta per a diversos conjunts d’entrada. En primer lloc, dissenyem un mitjà subtractor i després aquest mòdul s’utilitza per implementar un subtractor complet. Per implementar això, fem servir la porta OR per combinar el o / ps per a la variable de Bout. El codi de registre del subtractor complet es mostra a continuació

mòdul o_gate (a0, b0, c0)

entrada a0, b0

sortida c0

assignar c0 = a0 | b0

endmodule

mòdul xor_gate (a1, b1, c1)

entrada a1, b1

sortida c1

assignar c1 = a1 ^ b1

endmodule

mòdul and_gate (a2, b2, c2)

entrada a2, b2

sortida c2

assignar c2 = a2 & b2

endmodule

mòdul not_gate (a3, b3)

entrada a3

sortida b3

assigna b3 = ~ a3

endmodule

mòdul half_subtractor (a4, b4, c4, d4)

entrada a4, b4

sortida c4, d4

filferro x

xor_gate u1 (a4, b4, c4)

and_gate u2 (x, b4, d4)

not_gate u3 (a4, x)

endmodule

mòdul full_subtractor (A, B, Bin, D, Bout)

entrada A, B, Bin

sortida D, Bout

filferro p, q, r

half_subtractor u4 (A, B, p, q)

half_subtractor u5 (p, Bin, D, r)

o_gate u6 (q, r, Bout)

endmodule

Subtractor complet amb multiplexor 4X1

L’execució de la resta es pot fer mitjançant el mètode del complement dels dos. Per tant, necessitem utilitzar una porta 1-XOR que s'utilitzi per invertir 1 bit i incloure'n un al bit de transport. La sortida de DIFERÈNCIA és similar a la sortida SUM en el circuit de sumador complet, tot i que la BARROW o / p no és similar a la sortida de transport de la suma de sumador tot i que és invertida i complementada, com A - B = A + (-B) = Complement de A + dos de B.

El disseny d’aquest amb multiplexor 4X1 es mostra al següent diagrama lògic. Aquest disseny es pot fer seguint els passos següents.

Multiplexor 4X1

- Al pas 1, hi ha dues sortides com Sub i Borrow. Per tant, hem de triar 2 multiplexors.

- Al pas 2, la taula de veritat es pot implementar juntament amb K-maps

- Al pas 3, es poden seleccionar les dues variables com a línia de selecció. Per exemple, el B & C és en aquest cas.

Taula de la Veritat

El taula de veritat del subtractor complet El circuit que utilitza multiplexor 4X1 inclou el següent

A | B | C | Sub | Préstec |

0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

Subtractor complet mitjançant el descodificador

El disseny d’un subtractor complet mitjançant 3 a 8 descodificadors es pot fer mitjançant sortides actives baixes. Suposem que funciona el descodificador mitjançant el següent diagrama lògic. El descodificador inclou tres entrades en 3-8 descodificadors. Basant-nos en la taula de veritat, podem escriure els terminis per als resultats de la diferència i el préstec.

De la taula de veritat anterior,

Per a les diferents funcions de la taula de veritat, els terminis es poden escriure com a 1,2,4,7 i, de manera similar, per al préstec, els terminis es poden escriure com a 1,2,3,7. Els descodificadors 3-8 inclouen tres entrades i 8 sortides de 0 a 7 números.

Descodificador de 3 a 8

Si l’entrada del subtractor és 000, la sortida ‘0’ estarà activa i, si l’entrada és 001, la sortida ‘1’ estarà activa.

Ara les sortides del subtractor es poden prendre de 1, 2, 4 i 7 per connectar-lo a una porta NAND, llavors la sortida serà la diferència. Aquestes sortides es poden connectar a altres portes lògiques NAND on la sortida canvia al préstec.

Per exemple, si l'entrada és 001, la sortida serà 1 que significa que està activa. Per tant, la sortida està activa baixa i la sortida es pot obtenir des de la porta NAND anomenada funció diferencial com alta i la funció de préstec també canvia a ser alta. Per tant, obtenim la sortida preferida. Finalment, el descodificador funciona com un subtractor complet.

Avantatges i inconvenients

El avantatges del subtractor inclou el següent.

- El disseny de subtractor és molt senzill, així com implementar

- Deducció de potència dins de DSP (processament de senyal digital)

- Les tasques computacionals es poden realitzar a gran velocitat.

El desavantatges del subtractor inclou el següent.

- A la meitat de substracte, no hi ha cap condició per acceptar dades similars a les de la fase anterior.

- La velocitat del subtractor pot ser parcial a través del retard en el circuit.

Aplicacions

Alguns dels aplicacions de subtractor complet inclou el següent

- Aquests s'utilitzen generalment per ALU (unitat lògica aritmètica) en ordinadors per restar com a CPU i GPU les aplicacions de gràfics per disminuir la dificultat del circuit.

- Els restants s'utilitzen principalment per realitzar funcions aritmètiques com la resta, en calculadores electròniques i dispositius digitals.

- Aquests també són aplicables a diferents microcontroladors per a la resta aritmètica, temporitzadors i el comptador de programes (PC)

- Els subtractors s’utilitzen en processadors per calcular taules, adreces, etc.

- També és útil per a sistemes basats en xarxes i DSP.

- S’utilitzen principalment per ALU dins d’ordinadors per restar com CPU i GPU aplicacions gràfiques per reduir la complexitat del circuit.

- S’utilitzen principalment per realitzar funcions aritmètiques com la resta en dispositius digitals, calculadores, etc.

- Aquests subtractors també són apropiats per a diversos microcontroladors per temporitzadors, PC (comptador de programes) i restes aritmètiques

- S’utilitzen per als processadors per calcular adreces, taules, etc.

- La implementació d'això amb portes lògiques com NAND i NOR es pot fer amb qualsevol circuit lògic de subtractor complet, ja que les portes NOR i NAND es diuen portes universals.

A partir de la informació anterior, en avaluar el sumador, el subtractor complet mitjançant dos circuits de mitges subtractores i les seves formes tabulars, es pot notar que Dout en el subtractor complet és exactament similar al Sout del sumador complet. L'única variació és que A (variable d'entrada) es complementa en el subtractor complet. Per tant, és possible canviar el circuit de sumador complet en un restador complet només complementant l’i / p A abans de donar-lo a les portes lògiques per generar la darrera sortida de bit de préstec (Bout).

Mitjançant l'ús de qualsevol circuit lògic de subtractor complet, es pot implementar el subtractor complet que utilitza portes NAND i el subtractor complet que utilitza nor portes, ja que tant les portes NAND com NOR es tracten com portes universals. Aquí teniu una pregunta, quina diferència hi ha entre el mitjà subtractor i el subtractor complet?