En aquest article estudiarem un disseny de cronòmetre digital configurat al voltant del popular IC LM555 juntament amb un comptador IC de 4 dígits amb controladors de sortida multiplexats de 7 segments (MM74C926).

Escrit i enviat per: Jennifer Goldy

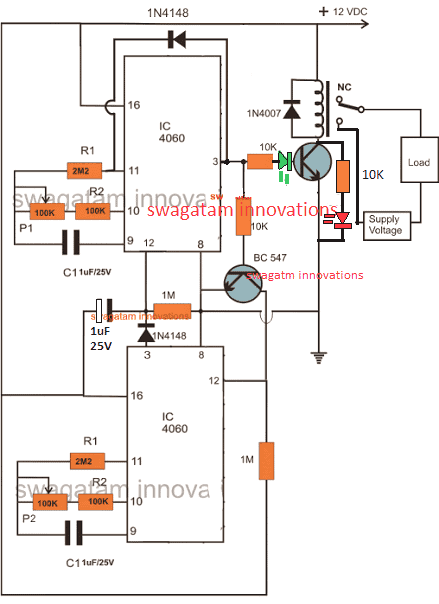

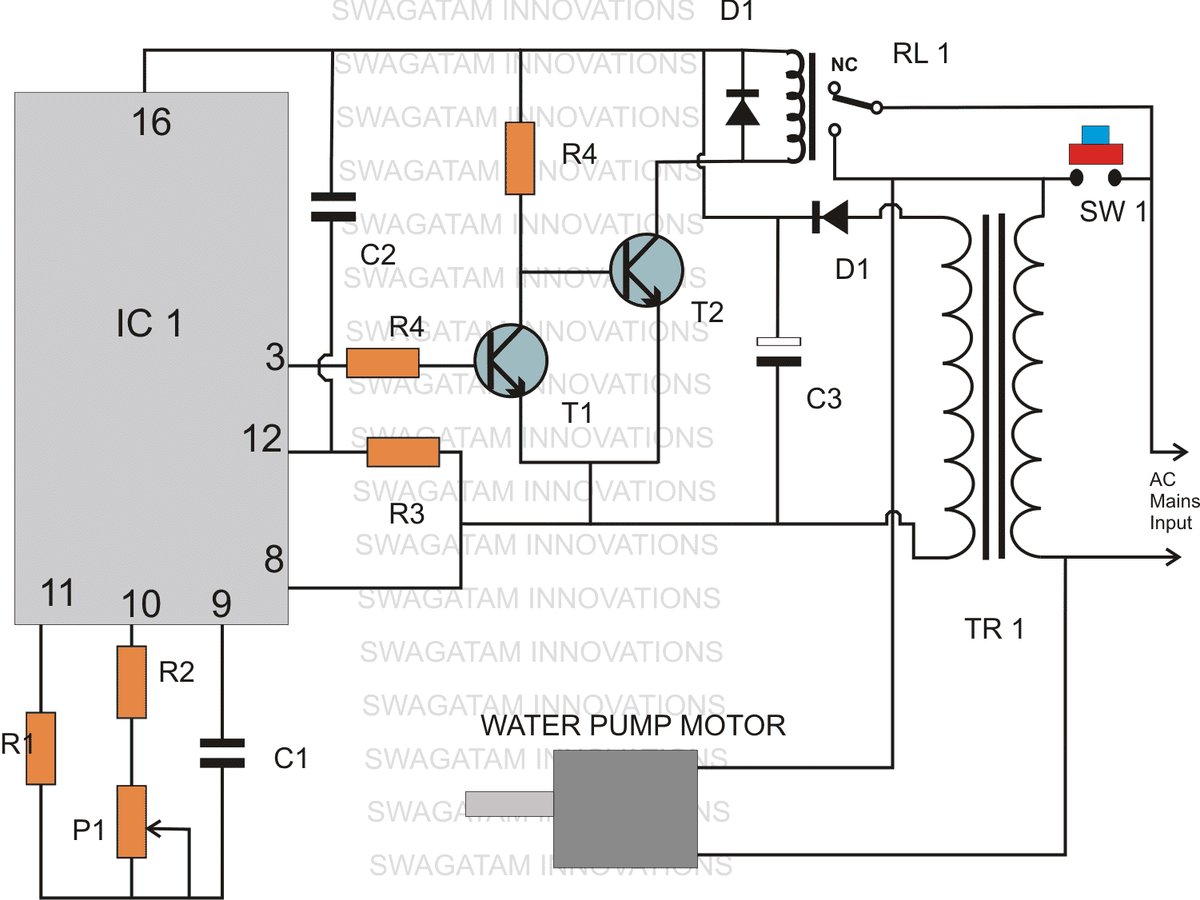

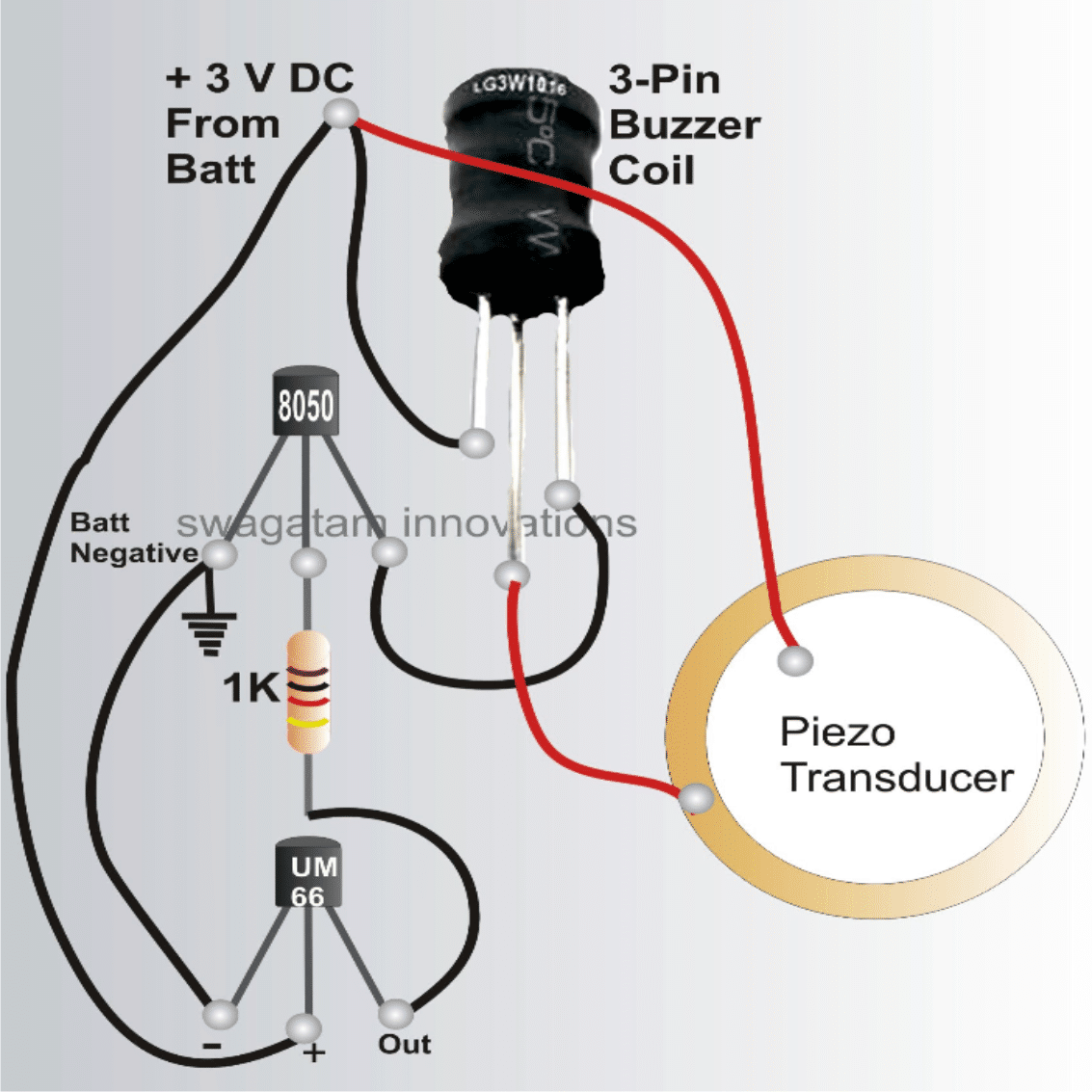

Funcionament del circuit

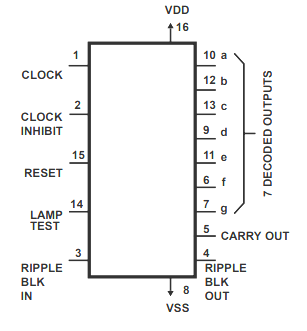

IC MM74C926 està format internament per un comptador de 4 dígits, una etapa de bloqueig de sortida, una sortida npn responsable de proveir xarxes de controladors per a càtodes comuns, pantalla de 7 segments i un circuit de multiplexació intern amb quatre sortides de multiplexació.

L’etapa del circuit de multiplexació també inclou un oscil·lador de funcionament lliure integrat i no es basa en cap xarxa de generació de freqüència externa addicional.

El comptador està dissenyat per procedir a una pujada negativa dels senyals del rellotge.

El senyal de rellotge és fabricat pel temporitzador IC LM555 (IC1) i impressionat al pin 12 de IC2.Un senyal més alt al pin de restabliment 13 de IC2 restableix la IC a la lògica zero.

El pin de restabliment 13 s'associa amb + 5V mitjançant un interruptor de reinici S3.

En el moment que es prem S2 fins i tot durant una fracció de segon, la xifra de recompte es converteix en una lògica zero, el transistor T1 respon amb un activador i es reinicia IC1.

Això imposa el recompte per començar en una situació en què S2 es troba en estat 'off'.

Esquema de connexions

Un senyal lògic baix al pin d’entrada de bloqueig 5 (LE) de l’IC2 bloqueja el recompte del mòdul de comptador als tancaments de sortida del conjunt de xips.

En cas que l’interruptor S2 estigui engegat, el pin 5 es veu obligat a baixar i, per tant, es permet guardar la xifra de recompte a la secció de pestell de l’IC.

El pin 6 (DS) de selecció de pantalla determina si la figura del comptador o el recompte emmagatzemat al pestell es poden mostrar o no a la pantalla.

En cas que el pin 6 es mantingui baix, la figura de la secció de pestell de sortida està habilitada per mostrar-se, però si el pin 6 es representa amb una lògica elevada, el recompte emmagatzemat al comptador s’il·lumina a la pantalla connectada.

En una ocasió en què es commuta l’interruptor S2, la base del transistor pnp T2 s’uneix a terra garantint que comenci a funcionar. L'emissor de T2 està equipat amb el pin DS d'IC2.

En conseqüència, sempre que l’interruptor S3 estigui engegat, el pin de restabliment 13 de l’IC2 s’acobla amb el negatiu a través del transistor T1 assegurant-se que l’oscil·lador està inhibit per generar impulsos de rellotge. Aquesta operació s'executa per implementar una sincronització entre IC1 i IC2.

Al primer nivell, restableix el mòdul per tal que la pantalla mostri ‘0000.’ A continuació, desconnecta l’interruptor S2 del cronòmetre per iniciar el recompte dels punts. En cas que vulgueu inhibir el rellotge del xip, simplement desactiveu el control S2.

Es pot optar per l'interruptor rotatiu donat S1 per seleccionar els diferents intervals de temps a la sortida del multivibrador astable (IC1).

El circuit de cronòmetre digital proposat funcionarà amb entrades de subministrament de 5V. El circuit es pot fixar fàcilment i construir sobre un PCB d’ús general.

És possible que vulgueu incloure tot el circuit en un armari metàl·lic amb ranures construïdes per a quatre pantalles de 7 segments, l’interruptor rotatiu S1, l’interruptor d’arrencada / parada S2 i l’interruptor de reinici S3 a la placa del tauler del tancador seleccionat.

Anterior: rellotge digital simple amb circuit IC LM8650 Següent: Com interactuar Arduino PWM amb qualsevol inversor