El processador MicroBlaze es va desenvolupar l'any 2002 per integrar diverses funcions complicades per satisfer la demanda nova i creixent del mercat. Per tant, el processador MicroBlaze és un element essencial dins de la cartera de gamma baixa de Xilinx per permetre un desenvolupament més ràpid del sistema que conté Artix®-7. FPGA , Spartan®-6, Zynq®-7000 AP SoC. Aquest processador és extremadament configurable, de manera que es pot utilitzar com a processador o microcontrolador incrustat dins dels FPGA i també com a coprocessador als SoC Zynq-7000 AP basats en ARM Cortex-A9. Aquest article ofereix una breu informació sobre Processador MicroBlaze – arquitectura i treball amb aplicacions.

Què és el processador Microblaze?

El microprocessador suau que està dissenyat principalment per a FPGA de Xilinx es coneix com el processador MicroBlaze. Aquest processador simplement s'implementa dins del teixit lògic i de memòria de propòsit general dels FPGA de Xilinx. Aquest processador és similar a l'arquitectura DLX basada en RISC i té un sistema d'interconnexió flexible perquè admet diferents aplicacions incrustades. El bus d'E/S principal i la interconnexió AXI del MicroBlaze és un bus de transaccions assignat a memòria amb una instal·lació mestre-esclau.

MicroBlaze utilitza un bus LMB dedicat per accedir a la memòria local i proporciona un emmagatzematge ràpid al xip. Moltes parts d'aquest processador es poden configurar per l'usuari, com ara la mida de la memòria cau, la unitat de gestió de memòria de la profunditat de la canalització, els perifèrics incrustats i les interfícies de bus.

Característiques de Microblaze

El característiques de Microblaz i inclouen el següent. Té 32 registres d'ús general.

- Té paraules d'instrucció de 32 bits que inclouen 2 modes d'adreçament i 3 operands.

- El bus d'adreces és de 32 bits.

- Té una canonada de 3 etapes o una de 5 etapes.

- Una unitat de bloc ALU amb un canviador.

- L'arquitectura de Harvard inclou dades de 32 bits i bus d'adreces.

- Interfície de dades i instruccions de bus de memòria local o LMB.

- Interfícies de flux AX14 i AX14.

- Unitat de coma flotant i unitat de gestió de memòria.

- Admet lockstep.

- Interfície de depuració i traça.

Arquitectura Microbaze

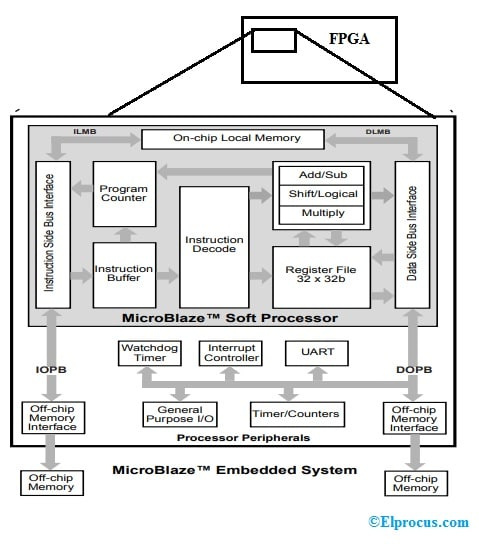

A continuació es mostra el diagrama de blocs del processador MicroBlaze. Aquest processador MicroBlaze és extremadament personalitzable i admet més de 70 opcions de disseny. Aquesta arquitectura mostra funcions de maquinari permanents, així com opcions configurables com la memòria cau d'instruccions o dades, la unitat de gestió de memòria, la unitat de coma flotant, etc.

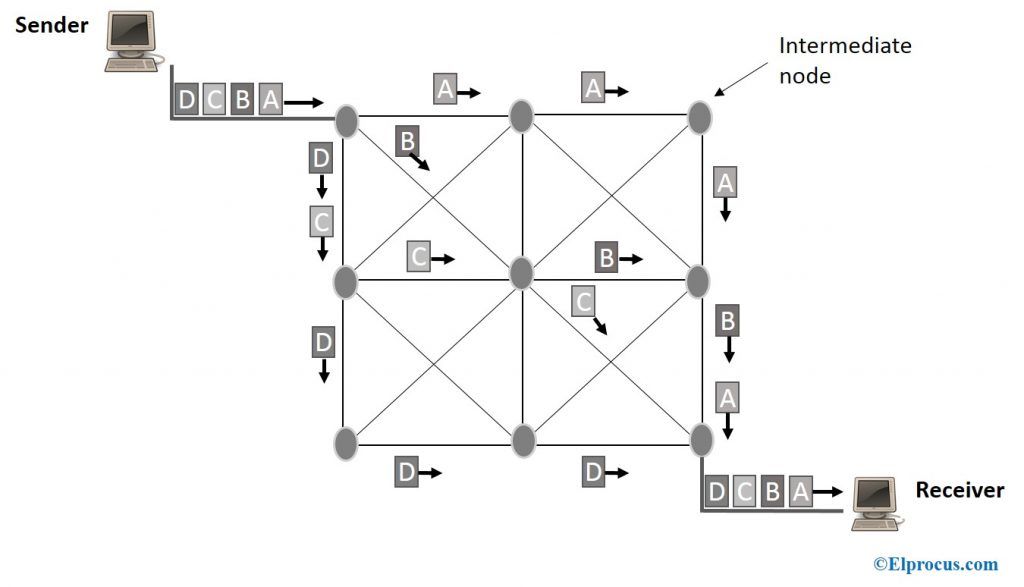

An sistema incrustat muntat al voltant d'un processador MicroBlaze inclou principalment MicroBlaze Soft Processor Core, memòria local en xip, interconnexions de bus estàndard i perifèrics OPB (bus perifèric en xip). Un sistema de processador MicroBlaze va principalment des d'un nucli de processador mitjançant una memòria local fins a un sistema gran que inclou diversos MicroBlaze processadors , memòria externa i molts perifèrics OPB.

Nucli de processador suau

El nucli del processador suau de MicroBlaze és fonamental per al sistema incrustat MicroBlaze. Aquest és un processador RISC de 32 bits molt ràpid i eficient que té les següents característiques.

- El conjunt d'instruccions és ortogonal.

- Busos de dades i d'instruccions separats.

- Registres de propòsit general de 32 bits.

- Té un canviador de canó complet opcional de 32 bits.

- Interfícies integrades per OCM ràpid o memòria en xip i OPB (On-chip Peripheral Bus) estàndard de la indústria d'IBM.

Les implementacions dins de Virtex-II i els dispositius posteriors admeten la multiplicació de maquinari.

Memòria local al xip

La memòria síncrona és una memòria local que s'utilitza principalment per permetre la memòria RAM del bloc al xip.

Interconnexions d'autobús estàndard

Les interfícies de bus al costat d'instruccions i dades inclouen una interfície a la memòria local que s'anomena LMB (Local Memory Bus) i una interfície al bus perifèric on-chip d'IBM. Per tant, podem dissenyar sistemes que s'adhereixin estrictament a l'arquitectura de Harvard, en cas contrari, per compartir recursos, podem utilitzar un únic OPB en combinació mitjançant un àrbitre d'autobús.

El bus de memòria local ofereix una entrada segura d'un sol cicle per a la memòria RAM de blocs en xip. Aquest és un protocol de bus molt eficient, senzill i d'un sol mestre i és perfecte per connectar memòria local ràpida. L'OPB o On-Chip Peripheral Bus és un bus multimaster ample de 32 bits que és perfecte per unir perifèrics i memòria exterior al nucli del processador MicroBlaze.

Perifèrics de bus perifèrics en xip

El sistema de maquinari MicroBlaze es completa amb perifèrics OPB per oferir diferents funcions com Watchdog Timer o Timebase, General purpose Timer or Counters, IC (Interrupt Controller), diferents controladors com SRAM, Flash Memory, ZBT Memory, BRAM, DDR, SDRAM, UART Lite , SPI, I2C, E/S de propòsit general, UART 16450/550 i Ethernet 10/100 MAC. A més, també podem afegir i definir perifèrics principalment per a funcions personalitzades, en cas contrari, una interfície a un disseny que existeix a l'FPGA.

Conjunt d'instruccions Microblaze

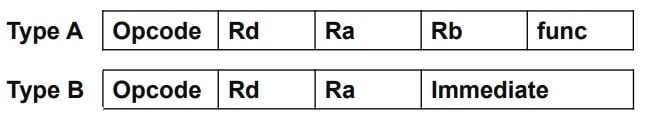

Els conjunts d'instruccions de Microblaze són aritmètica, lògica, branca, càrrega/emmagatzemament i altres. La mida de totes les instruccions és fixa. Com a màxim es poden donar 3 registres com a operands. Microblaze inclou dos formats d'instruccions tipus A i tipus B que es mostren a continuació.

El format d'instrucció de tipus A s'utilitza principalment per a instruccions de registre-registre. Per tant, inclou el codi operatiu, una destinació única i dos registres d'origen. El format d'instrucció de tipus B s'utilitza principalment per a instruccions de registre immediat que inclouen el codi operatiu, la destinació única i els registres d'origen únic. i una font de valor immediat de 16 bits.

En els dos formats d'instrucció anteriors, el codi operatiu és un codi d'operació, Rd és un registre de destinació que està codificat amb 5 bits, Ra i Rb són registres font on cadascun està codificat amb 5 bits i Immediat és un valor de 16 bits.

Instruccions aritmètiques

Les instruccions aritmètiques de tipus A i B es donen a continuació.

Tipus A

|

ADD Rd, Ra, Rb afegir |

Rd = Ra+Rb, bandera de transport afectada |

|

ADD K Rd, Ra, Rb Afegeix i mantén el transport |

Rd = Ra+Rb, bandera de transport no afectada |

| RSUB Rd, Ra, Rb Resta inversa |

Rd = R-Rb, la bandera de transport no està afectada |

Tipus B

|

ADD I Rd, Ra, Imm afegir immediatament |

Rd = Ra+signExtend32 (Imm) |

|

ADD IK Rd, Ra, Imm afegir immediata i mantenir portar |

Rd = Ra+ signeExtend32 (Imm) |

| RSUBIK Rd, Ra, Imm resta inversa amb immediata |

Rd = Ra+ signeExtend32 (Imm) -Ra |

| SRA Rd, Ra desplaçament aritmètic a la dreta |

Rd = (Ra>>1) |

Instruccions lògiques

Les instruccions lògiques de tipus A i B es donen a continuació.

Tipus A

|

O Rd, Ra, Rb Lògic o |

Rd = Ra| Rb |

|

I Rd,Ra,Rb Addició lògica |

Rd = Ra i Rb |

| XOR Rd, Ra, Rb Xor logològic |

Rd = Rb ^ Rb |

| ANDN Rd, Ra, Rb Lògic i no |

Rd = Ra i (Rb) |

Tipus B

|

ORI Rd, Ra, Imm OR lògic amb immediat |

Rd = Ra | signExtend32 (Imm) |

| ANDI Rd, Ra, Imm lògic I amb immediat |

Rd = Ra i signExtend32 (Imm) |

| XORI Rd, Ra, Imm XOR logoical amb immediat |

Rd = Ra ^ signExtend32 (Imm) |

| ANDNI Rd, Ra, Imm Lògic I NO amb immediat |

Rd = Ra & (signExtend32 (Imm)) |

Instruccions de la sucursal: incondicional

Modifiqueu el registre del comptador de programes

| BID Imm sucursal immediata amb retard immediat |

PC = PC+ signeExtend32 (Imm) permetre l'execució de la ranura de retard |

| BRLID Rd, Imm sucursal i enllaç immediat amb retard immediat (trucada de funció) |

Rd = PC PC = PC+& signExtend32 (Imm) permetre l'execució de la ranura de retard |

| RTSD Ra, Imm retorn de la subrutina |

PC = Ra + signExtend32 (Imm) permetre l'execució de la ranura de retard |

| RTID Ra, Imm retorn de la interrupció |

PC = Ra + signExtend32 (Imm) permetre l'execució de la ranura de retard establiu l'habilitat d'interrupció a MSR |

Instruccions de la sucursal: incondicional1

Canvieu el registre del comptador de programes quan es compleixi una condició

| BEQI Ra, Imm branca si és igual |

PC = PC+ signeExtend32 (Imm) Si Ra = = 0 |

| MASH Ra, Imm branca si no és igual |

Rd = PC PC = PC+& signExtend32 (Imm) Si Ra! = 0 |

Instruccions de la sucursal: incondicional2

Canvieu el registre del comptador de programes quan es compleixi una condició

| BLTI Ra, Imm branca si és inferior a |

PC = PC+ signeExtend32 (Imm) Si Ra < 0 |

| BLEI Ra, Imm branca si és inferior igual que |

Rd = PC PC = PC+& signExtend32 (Imm) Si Ra!< = 0 |

| BGTI Ra, Imm branca si és més gran que |

PC = PC+ signeExtend32 (Imm) Si Ra!> 0 |

| BGEI Ra, Imm branca si és més gran que |

PC = PC+signExtend32 (Imm) Si Ra!>= 0 |

Instruccions de càrrega/emmagatzematge -Tipus A

| LW Rd, Ra, Rb Carrega la paraula |

Adreça = Ra+Rb Rd = *Adreça |

| Carrer SW, Ra, Rb Emmagatzema word |

Adreça – Ra+Rb * Adreça = Rd |

Tipus B

| LWI Rd, Ra, Imn Carregueu la paraula immediatament |

Adreça = Ra + signExtend32 (Imm) Rd = *Adreça |

| SW Rd, Ra, Imm Emmagatzema la paraula immediatament |

Adreça = Ra + signExtend32 (Imm) * Adreça = Rd |

Altres instruccions

| IMM, Imm immediat |

Amplieu l'Imm d'una instrucció de tipus B anterior a 32 bits. |

| MFS Rd, Sa Passar del registre de finalitats especials |

Rd = Sa Sa- registre de propòsit especial, operand font

|

| MTS Sd, Ra Passar al registre de propòsits especials |

Sd = Ra Sd: registre de propòsit especial, operand de destinació |

Registres

L'arquitectura del processador MicroBlaze és completament ortogonal, que inclou registres de propòsit general de 32 bits i registres de propòsit especial de 32 bits com ara el comptador de programes i el registre d'estat de la màquina.

Arquitectura de canonades

MicroBlaze utilitza una arquitectura de canalització de 3 etapes que inclou les etapes de recuperació, descodificació i completa. Automàticament, el reenviament de dades, les sucursals i la parada de la canalització es determinen dins del maquinari.

Arquitectura de càrrega o emmagatzematge

MicroBlaze admet memòria en tres mides de dades: 8 bits (byte), 16 bits (mitja paraula) i 32 bits (paraula). Per tant, els accessos a la memòria estan sempre alineats a la mida de les dades. Aquest és un processador Big-Endian que utilitza l'adreça de l'adreça Big-Endian així com les convencions d'etiquetatge un cop accedeix a la memòria.

Interrupcions

Un cop es produeix una interrupció, aquest processador finalitzarà l'execució actual per gestionar la sol·licitud d'interrupció mitjançant la ramificació per interrompre l'adreça del vector i emmagatzemar l'adreça d'instrucció que cal executar. Aquest processador aturarà les interrupcions futures esborrant la marca IE (Interrupt Enable) dins del MSR (Machine Status Register).

Com funciona Microblaze?

El processador MicroBlaze admet una amplada de bus de 32 bits i aquest nucli del processador és un motor basat en RISC que inclou un fitxer de registre basat en RAM LUT de 32 bits mitjançant instruccions separades per a l'accés a la memòria i les dades.

Aquest processador només admet tant BlockRAM en xip com memòria externa. Similar a l'IBM PowerPC; tots els perifèrics utilitzen el bus CoreConnect OPB similar; els perifèrics del processador estan ben combinats amb PowerPC a Virtex-II Pro.

El processador MicroBlaze ofereix una flexibilitat total per triar la combinació de funcions de memòria, perifèrics i interfície que us proporcionaran el sistema precís que necessiteu en una única FPGA amb menys cost.

Diferència B/N Microblaze vs Risc-V

El diferència entre MicroBlaze i RISC v incloure el següent.

|

Microblaze |

Risc-V |

| És un nucli de microprocessador suau dissenyat principalment per a Xilinx FPGA.

|

RISC-V és una arquitectura de conjunt d'instruccions arrelada en els principis RISC.

|

| Utilitza l'arquitectura RISC de Harvard. | Utilitza l'arquitectura del conjunt d'instruccions. |

| La seva llicència és propietat (Xilinx) | La seva llicència és de codi obert. |

| La profunditat de la canonada és de 3 o 5. | La profunditat de la canonada és de 5. |

| El seu rendiment és de 280 DMIP. | El seu rendiment és de 250 DMIP. |

| La seva velocitat és de 235 MHz. | La seva velocitat és de 250 MHz. |

| Té 1027 LUT. | Té 4125 LUT. |

| La implementació de la tecnologia utilitzada és Xilinx FPGA. | La implementació de la tecnologia utilitzada és FPGA/ASIC. |

Avantatges de Microblaze

El avantatges de MicroBlaze incloure el següent.

- És econòmic.

- És altament configurable.

- El seu rendiment és alt en comparació amb ARM.

- Compta amb un kit de desenvolupament integrat.

- És un suau microprocessador nucli.

- Per ajudar-vos a organitzar ràpidament la vostra aplicació, aquest processador inclou tres configuracions fixes relacionades amb les classes de processadors conegudes: microcontrolador, en temps real i processador d'aplicacions.

Aplicacions de Microblaze

El aplicacions de MicroBlaze incloure el següent.

- Aquest processador compleix molts requisits d'aplicació diferents com ara industrial, automotriu, mèdic i de consum, etc.

- Les aplicacions de MicroBlaze van des de màquines d'estat simples basades en programari fins a controladors complexos utilitzats en aplicacions incrustades o aparells basats en Internet.

- Està optimitzat per a aplicacions incrustades com el control industrial, l'ofimàtica i l'automoció.

- El MicroBlaze és capaç de comunicar-se amb un gran conjunt de perifèrics per adaptar-se a aplicacions a escala mitjana.

- La naturalesa suau d'aquest processador el fa personalitzable per a diferents aplicacions on els dissenyadors poden intercanviar funcions per mida per assolir els objectius de preu i rendiment per a aplicacions mèdiques, d'automoció, industrials i de seguretat.

Per tant, tot això es tracta una visió general del Microblaze processador. Aquest és un nucli de processador suau RISC programable de 32 bits amb totes les funcions. Aquest processador compleix diferents requisits dins de diferents camps com els mercats de consum, mèdic, industrial, automoció i d'infraestructura de comunicacions. És extremadament configurable, de manera que s'utilitza com a processador o microcontrolador incrustat dins dels FPGA, d'altra manera com un coprocessador per a l'ARM. Aquí teniu una pregunta per a vosaltres, què és FPGA?