Una etapa de memòria intermèdia bàsicament una etapa intermèdia reforçada que permet que el corrent d’entrada arribi a la sortida sense que es vegi afectat per la càrrega de sortida.

En aquest post intentarem entendre què són els búfers digitals i veurem la seva definició, símbol, taula de veritat, doble inversió mitjançant la porta lògica “NO”, el búfer digital del ventilador, el búfer triestat equivalent de commutador de memòria intermèdia de tres estats, memòria intermèdia de tres estats 'HIGH' activa, memòria intermèdia de tres estats activa 'HIGH', memòria intermèdia de tres estats 'LOW' activa, memòria intermèdia de tres estats activa 'LOW', control de memòria intermèdia de tres estats , control de bus de dades de memòria intermèdia de tres estats i, finalment, farem una visió general de les memòries digitals de memòria intermèdia i de memòria intermèdia disponibles.

En una de les entrades anteriors vam aprendre sobre la porta lògica 'NO', que també s'anomena inversor digital. En una porta NO la sortida sempre és complementària a l'entrada.

Per tant, si l'entrada és 'ALTA' la sortida es torna 'BAIXA', si l'entrada és 'BAIXA' la sortida es torna 'ALTA', de manera que s'anomena inversor.

Podria haver-hi una situació en què la sortida s’hagi de separar o aïllar de l’entrada, o en casos en què l’entrada pugui ser força feble i necessiti conduir càrregues que requereixin un corrent superior sense invertir la polaritat del senyal mitjançant un relé o transistor, etc. En aquestes situacions, els búfers digitals es fan útils i s’apliquen efectivament com a búfers entre la font del senyal i l’etapa real del controlador de càrrega.

Tal portes lògiques que pot emetre la sortida de senyal igual que l'entrada i actuar com a etapa intermedia de memòria intermèdia s'anomena memòria intermèdia digital.

Un buffer digital no realitza cap inversió del senyal alimentat i tampoc no és un dispositiu de 'presa de decisions', com la porta lògica 'NO', sinó que dóna la mateixa sortida que l'entrada.

Il·lustració de Digital Buffer:

El símbol anterior és similar a la porta lògica 'NO' sense la 'o' a la punta del triangle, el que significa que no realitza cap inversió.

L'equació booleana per a la memòria intermèdia digital és Y = A.

'Y' és l'entrada i la sortida 'A'.

Taula de veritat:

Doble inversió mitjançant portes lògiques 'NO':

Es pot construir una memòria intermèdia digital utilitzant dues portes lògiques “NO” de la manera següent:

El senyal d’entrada s’inverteix primer per la primera porta NOT del costat esquerre i el senyal invertit s’inverteix posteriorment per la següent porta “NOT” del costat dret, cosa que fa que la sortida sigui la mateixa que l’entrada.

Per què s’utilitzen els buffers digitals

Ara és possible que us rasqueu el cap per què fins i tot existeix la memòria intermèdia digital, no fa cap operació com altres portes lògiques, només podríem llançar la memòria intermèdia digital d’un circuit i connectar un tros de filferro ... correcte? Doncs no realment.

Aquí teniu la resposta : Una porta lògica no requereix un corrent elevat per realitzar cap operació. Només requereix un nivell de tensió (5V o 0V) amb un corrent baix.

Tots els tipus de portes lògiques admeten principalment un amplificador integrat de manera que la sortida no depengui dels senyals d'entrada. Si en cascada dues portes lògiques 'NO' en sèrie obtindrem la mateixa polaritat del senyal que l'entrada al pin de sortida, però, amb un corrent relativament superior. En altres paraules, el buffer digital funciona com un amplificador digital.

Una memòria intermèdia digital es pot utilitzar com a etapa d’aïllament entre les etapes del generador de senyals i les etapes del controlador, també ajuda a evitar que la impedància afecti un circuit d’un altre.

Un buffer digital pot proporcionar una major capacitat de corrent que es pot utilitzar per conduir transistors de commutació de manera més eficient.

La memòria intermèdia digital proporciona una amplificació més elevada, que també s'anomena capacitat de 'ventilació'.

Capacitat de ventilació del buffer digital:

FAN-OUT : El ventilador es pot definir com el nombre de portes lògiques o ICs digitals que poden ser accionats en paral·lel mitjançant un buffer digital (o qualsevol IC digital).

Un buffer digital típic té un ventilador de 10, cosa que significa que el buffer digital pot gestionar 10 circuits digitals digitals en paral·lel.

FAN-IN : El ventilador és el nombre d’entrades digitals que la porta lògica digital o l’IC digital poden acceptar.

A l'esquema anterior, el buffer digital té un ventilador d'1, el que significa una entrada. Una porta 'I' de lògica de '2 entrades' té un ventilador de dos, etc.

Des de l'esquema anterior es connecta un buffer a les 3 entrades de tres portes lògiques diferents.

Si només connectem un tros de cable al lloc de la memòria intermèdia del circuit anterior, és possible que el senyal d’entrada no tingui prou corrent i faci caure tensió a través de les portes i que ni tan sols reconeixi el senyal.

Així, en conclusió, s’utilitza un buffer digital per amplificar un senyal digital amb una sortida de corrent superior.

Tampó de tres estats

Ara sabem què fa un buffer digital i per què existeix als circuits electrònics. Aquests buffers tenen dos estats 'HIGH' i 'LOW'. Hi ha un altre tipus de memòria intermèdia anomenada 'memòria intermèdia de tres estats'.

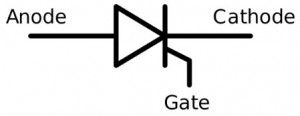

Aquest buffer té un pin addicional anomenat 'Activa el pin'. Mitjançant el pin d'activació podem connectar o desconnectar la sortida de l'entrada electrònicament.

Igual que un buffer normal, funciona com a amplificador digital i proporciona el mateix senyal de sortida que el senyal d’entrada, l’única diferència és que la sortida es pot connectar i desconnectar electrònicament mitjançant el pin d’activació.

Així doncs, s’introdueix un tercer estat, en aquest cas la sortida no és “ALTA” ni “BAIXA”, sinó un estat de circuit obert o alta impedància a la sortida i no respondrà als senyals d’entrada. Aquest estat es coneix com 'HIGH-Z' o 'HI-Z'.

L'anterior és el circuit equivalent del buffer triestat. El pin d'activació pot connectar o desconnectar la sortida de l'entrada.

Hi ha quatre tipus de memòria intermèdia de tres estats:

• Búfer actiu de tres estats 'HIGH' actiu

• Búfer actiu de tres estats 'BAIX' actiu

• Memòria intermèdia activa de tres estats 'HIGH' activa

• Búfer actiu d'inversió de tres estats 'BAIX'

Vegem cadascun d’ells seqüencialment.

Búfer actiu de tres estats 'HIGH' actiu

A la memòria intermèdia activa “HIGH” (per exemple: 74LS241), el pin de sortida es connecta al pin d’entrada quan apliquem “HIGH” o “1” o senyal positiu al pin d’activació.

Si apliquem “BAIX” o “0” o senyal negatiu al pin d’activació, la sortida es desconnecta de l’entrada i passa a l’estat “HI-Z” on la sortida no respondrà a l’entrada i la sortida estarà en estat de circuit obert.

Memòria intermèdia activa de tres estats 'BAIX'

Aquí la sortida es connectarà a l'entrada quan apliquem 'BAIX' o '0' o senyal negatiu al pin d'activació.

Si apliquem el senyal “HIGH” o “1” o positiu per habilitar el pin, la sortida es desconnectarà de l'entrada i la sortida estarà en estat “HI-Z” / estat de circuit obert.

Taula de veritat:

Búfer actiu d'inversió de tres estats 'HIGH' actiu

A la memòria intermèdia activa de tres estats 'HIGH' activa (exemple: 74LS240), la porta actua com a porta lògica 'NO' però, amb el pin d'activació.

Si apliquem 'HIGH' o '1' o senyal positiu a l'entrada d'habilitació, la porta s'activa i actua com una porta lògica regular 'NO' on la seva sortida és inversió / complementària de l'entrada.

Si apliquem “BAIX” o “0” o senyal negatiu al pin d’activació, la sortida estarà en estat “HI-Z” o de circuit obert.

Taula de veritat:

Búfer actiu d'inversió de tres estats 'BAIX':

En el buffer actiu d'inversió de tres estats 'BAIX', la porta actua com a porta lògica 'NO' però, amb el pin d'activació.

Si apliquem 'BAIX' o '0' o senyal negatiu per habilitar el pin, la porta s'activa i funciona com una porta lògica normal 'NO'.

Si apliquem “HIGH” o “1” o senyal positiu per habilitar el pin, el pin de sortida estarà en estat “HI-Z” / estat de circuit obert.

Taula de veritat:

Control de memòria intermèdia de tres estats:

Per l'anterior, vam veure que un buffer pot proporcionar amplificació digital i que els buffers triestats poden desconnectar completament la seva sortida de l'entrada i donar un estat de circuit obert.

En aquesta secció coneixerem l’aplicació del búfer triestat i com s’utilitza en circuits digitals per gestionar la comunicació de dades de manera eficient.

Als circuits digitals podem trobar un bus de dades / cables que transporten dades, transporten tota mena de dades en un sol bus per reduir la congestió del cablejat / reduir les traces de PCB i també reduir el cost de fabricació.

A cada extrem del bus, es connecten múltiples dispositius lògics, microprocessadors i microcontroladors que intenten comunicar-se simultàniament, cosa que crea una cosa anomenada contenció.

La controvèrsia es produeix en un circuit quan alguns dispositius d’un bus impulsen “HIGH” i alguns dispositius actuen “LOW” simultàniament, cosa que provoca un curtcircuit i causa danys en un circuit.

La memòria intermèdia de tres estats pot evitar tals contencions i enviar i rebre dades adequadament a través d’un autobús.

El buffer de tres estats s’utilitza per aïllar els dispositius lògics, microprocessadors i microcontroladors els uns dels altres en un bus de dades. Un descodificador permet que només un conjunt de memòries intermèdies triestatals passin dades a través del bus.

Digueu si el conjunt de dades 'A' està connectat a un microcontrolador, el conjunt de dades 'B' a un microprocessador i el conjunt de dades 'C' a alguns circuits lògics.

A l'esquema anterior, tots els búfers són búfers actius de tres estats actius.

Quan el descodificador estableix ENA 'HIGH', el conjunt de dades 'A' està habilitat, ara el microcontrolador pot enviar dades a través del bus.

La resta dels dos conjunts de dades “B” i “C” es troben en “HI-Z” o estat d’impedància molt alta que aïlla elèctricament el microprocessador i els circuits lògics del bus, que actualment utilitza el microcontrolador.

Quan el descodificador defineix ENB 'HIGH', el conjunt de dades 'B' pot enviar dades pel bus i la resta de conjunts de dades 'A' i 'C' estan aïllats del bus en estat 'HI-Z'. De la mateixa manera, quan el conjunt de dades 'C' està habilitat.

Qualsevol dels conjunts de dades 'A' o 'B' o 'C' utilitza el bus de dades en un moment determinat per evitar contenciós.

També podem establir comunicació dúplex (bidireccional) mitjançant la connexió de dos memòries intermèdies tri-estat en paral·lel i en direcció oposada. Els pins d'activació es poden utilitzar com a control de direcció. Per a aquest tipus d'aplicacions es pot utilitzar IC 74245.

A continuació, es mostra la llista de memòria intermèdia digital i memòria intermèdia triestat:

• Buffer hexagonal sense inversió 74LS07

• Buffer / controlador hexagonal 74LS17

• 74LS244 Octal Buffer / Line Driver

• Tampó bidireccional octal 74LS245

• Buffer hexagonal sense inversió CD4050

• CD4503 Hex Tri-state Buffer

• HEF40244 Buffer octal triestat

D’aquesta manera es conclou la nostra discussió sobre com funcionen els búfers digitals i les seves diverses configuracions digitals, espero que us hagi ajudat a entendre bé els detalls. Si teniu més preguntes o suggeriments, expresseu les vostres preguntes a la secció de comentaris, podreu obtenir una resposta ràpida.

Anterior: Com funcionen les portes lògiques Següent: Descripció de les resistències pull-up i pull-down amb diagrames i fórmules