Per a l'execució d'un programa d'ordinador, requereix el funcionament síncró de més d'un component d'un ordinador. Per exemple, Processadors - proporcionant la informació de control necessària, adreces ... etc, busos - per transferir informació i dades a i des de la memòria als dispositius d'E / S ... etc. El factor interessant del sistema seria la manera com gestiona la transferència d’informació entre el processador, la memòria i els dispositius d’E / S. Normalment, els processadors controlen tot el procés de transferència de dades, des de l'inici de la transferència fins a l'emmagatzematge de dades a la destinació. Això afegeix càrrega al processador i la major part del temps es manté en l’estat ideal, disminuint així l’eficiència del sistema. Per accelerar la transferència de dades entre dispositius d'E / S i memòria, el controlador DMA actua com a mestre d'estació. El controlador DMA transfereix dades amb la mínima intervenció del processador.

Què és un controlador DMA?

El terme DMA significa accés directe a la memòria. El dispositiu de maquinari utilitzat per a l'accés directe a la memòria s'anomena controlador DMA. DMA El controlador és una unitat de control , que forma part dels dispositius d'E / S circuit d'interfície , que pot transferir blocs de dades entre dispositius d'E / S i memòria principal amb la mínima intervenció del processador.

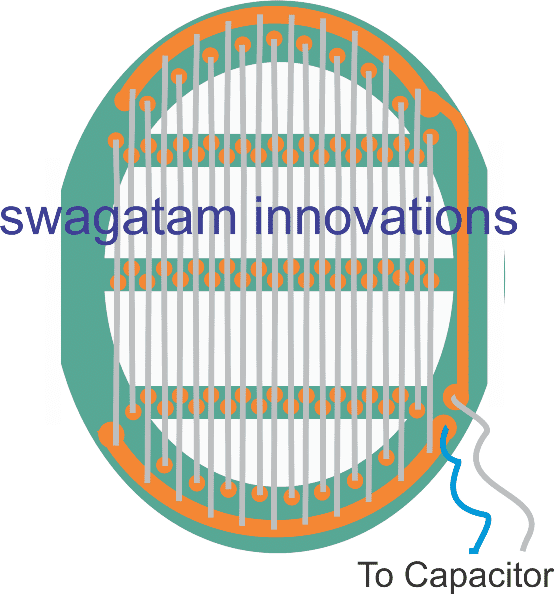

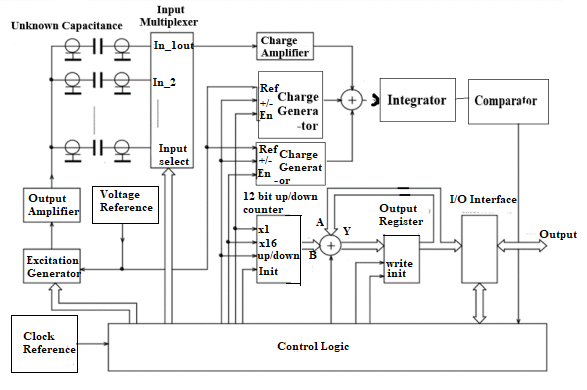

Diagrama del controlador DMA en arquitectura de computadors

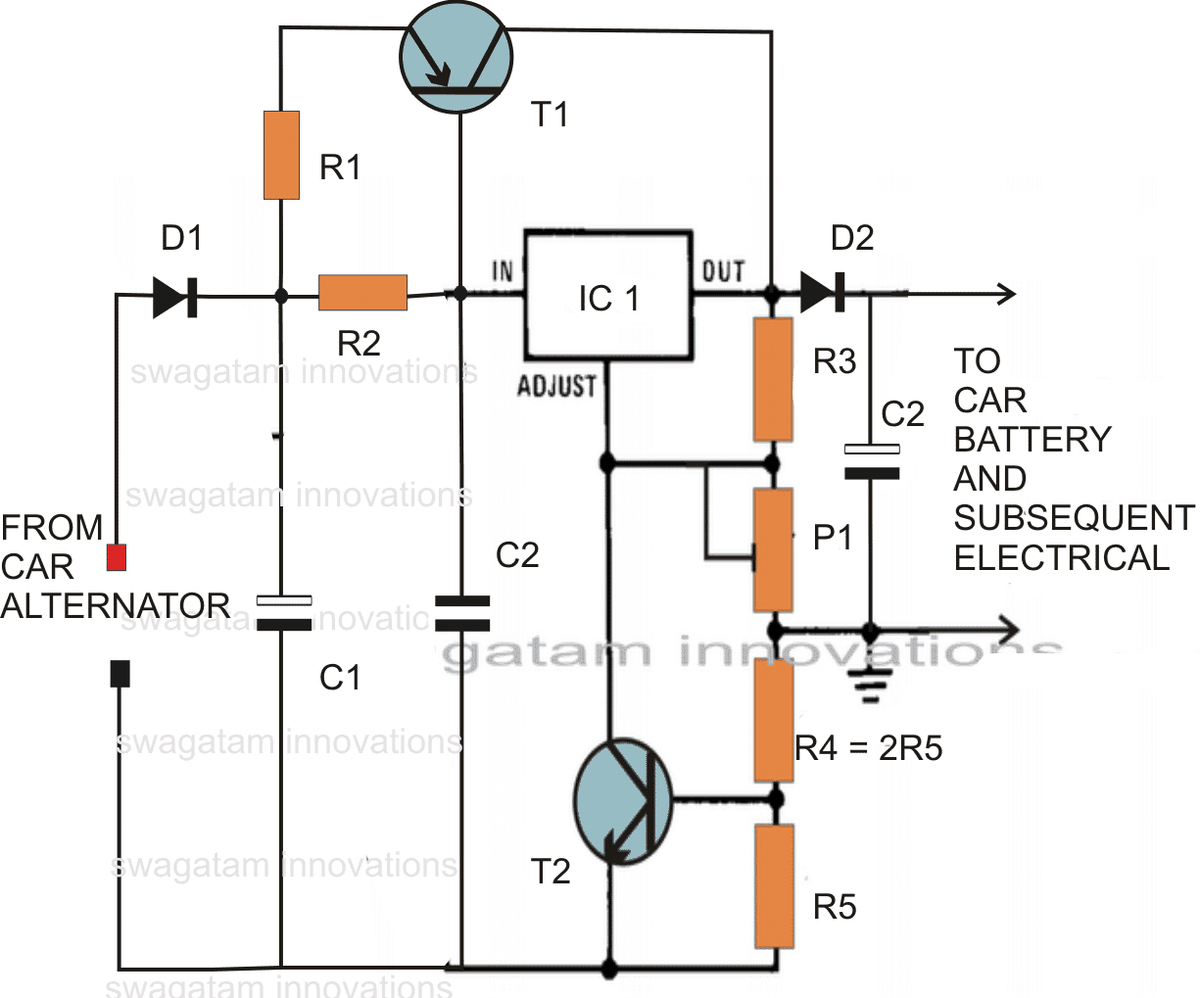

El controlador DMA proporciona una interfície entre el bus i els dispositius d’entrada-sortida. Tot i que transfereix dades sense la intervenció del processador, és controlat pel processador. El processador inicia el controlador DMA enviant l’adreça inicial, el nombre de paraules al bloc de dades i la direcció de transferència de dades, és a dir. des de dispositius d'E / S fins a la memòria o des de la memòria principal fins als dispositius d'E / S. Es poden connectar més d'un dispositiu extern al controlador DMA.

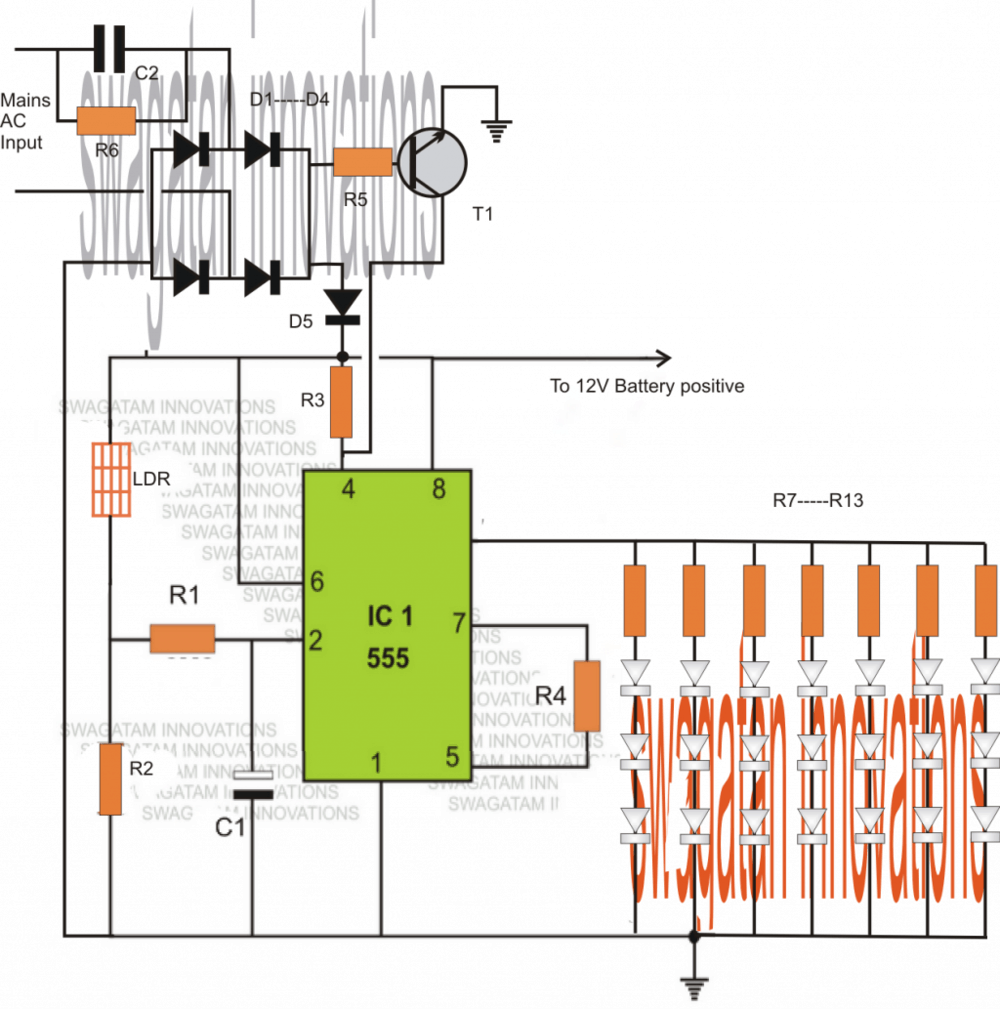

DMA en Arquitectura de Computadors

El controlador DMA conté una unitat d'adreces per generar adreces i seleccionar el dispositiu d'E / S per transferir. També conté la unitat de control i el recompte de dades per mantenir el recompte del nombre de blocs transferits i indicar el sentit de la transferència de dades. Quan es completa la transferència, DMA informa el processador mitjançant una interrupció. El diagrama de blocs típic del controlador DMA es mostra a la figura següent.

Diagrama de blocs típic del controlador DMA

Funcionament del controlador DMA

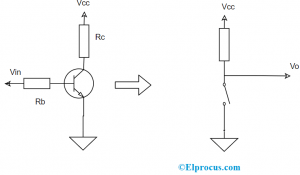

El controlador DMA ha de compartir el bus amb el processador per fer la transferència de dades. El dispositiu que sosté el bus en un moment determinat s’anomena bus master. Quan s'ha de fer una transferència des del dispositiu d'E / S a la memòria o viceversa, el processador atura l'execució del programa actual, incrementant el programa comptador, mou dades sobre la pila i envia un senyal de selecció DMA al controlador DMA a través del bus d’adreça.

Si el controlador DMA és lliure, sol·licita el control del bus al processador elevant el senyal de sol·licitud de bus. El processador concedeix el bus al controlador augmentant el senyal de concessió del bus, ara el controlador DMA és el mestre del bus. El processador inicia el controlador DMA enviant les adreces de memòria, el nombre de blocs de dades a transferir i la direcció de transferència de dades. Després d'assignar la tasca de transferència de dades al controlador DMA, en lloc d'esperar idealment fins a la finalització de la transferència de dades, el processador reprèn l'execució del programa després de recuperar les instruccions de la pila.

Transferència de dades a l’ordinador pel controlador DMA

El controlador DMA ara té el control total dels busos i pot interactuar directament amb memòria i dispositius d'E / S independents de la CPU. Realitza la transferència de dades segons les instruccions de control rebudes pel processador. Després de completar la transferència de dades, desactiva el senyal de sol·licitud de bus i la CPU desactiva el senyal de concessió del bus, movent així el control dels busos a la CPU.

Quan un dispositiu d'E / S vol iniciar la transferència, envia un senyal de sol·licitud DMA al controlador DMA, per al qual el controlador reconeix si és lliure. A continuació, el controlador sol·licita al processador el bus, elevant el senyal de sol·licitud de bus. Després de rebre el senyal de concessió del bus, transfereix les dades del dispositiu. Per a un controlador DMA canalitzat, es poden connectar un nombre de dispositius externs.

El DMA transfereix les dades en tres modes, que inclouen el següent.

a) Mode de ràfega : En aquest mode, DMA transmet els busos a la CPU només després de completar la transferència completa de dades. Mentrestant, si la CPU necessita el bus, ha de romandre ideal i esperar la transferència de dades.

b) Mode de robatori de cicle : En aquest mode, DMA proporciona el control dels busos a la CPU després de la transferència de cada byte. Emet contínuament una sol·licitud de control d’autobús, fa la transferència d’un byte i retorna l’autobús. Amb aquesta CPU no cal esperar molt de temps si necessita un bus per a tasques de prioritat superior.

c) Mode transparent: Aquí, DMA només transfereix dades quan la CPU executa la instrucció que no requereix l’ús de busos.

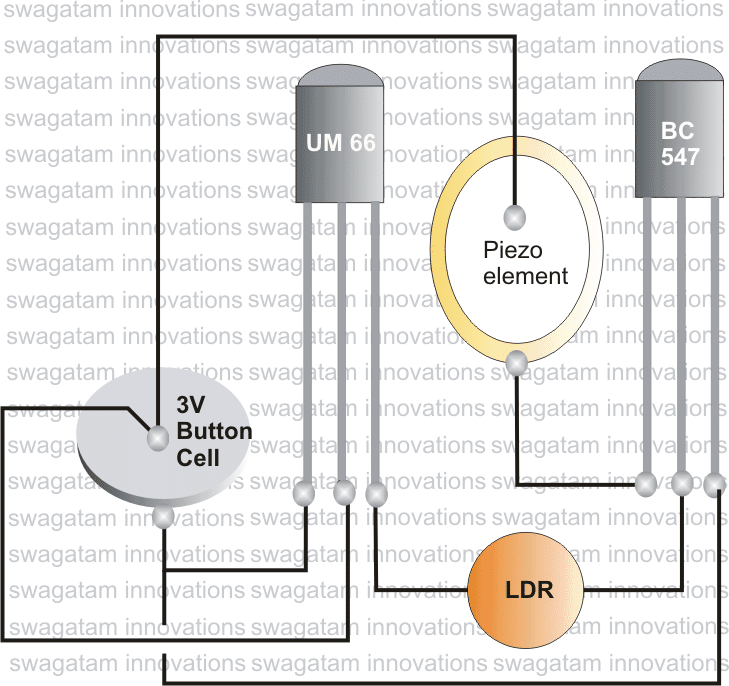

Controlador DMA 8237

- 8237 té 4 canals d'E / S juntament amb la flexibilitat d'augmentar el nombre de canals.

- Cada canal es pot programar individualment i té una adreça de 64 k i capacitat de dades.

- El bloc de control de sincronització, el bloc de control d’ordres de programa i el bloc de codificador prioritari són els tres blocs principals de 8237A.

- Els senyals de control intern i de control extern són conduïts pel bloc de control de temporització.

- Diverses ordres donades pel microprocessador al DMA són descodificades pel bloc de control d'ordres del programa.

- Quin canal s’ha de donar la màxima prioritat es decideix per la prioritat bloc de codificador .

8237A té 27 registres interns.

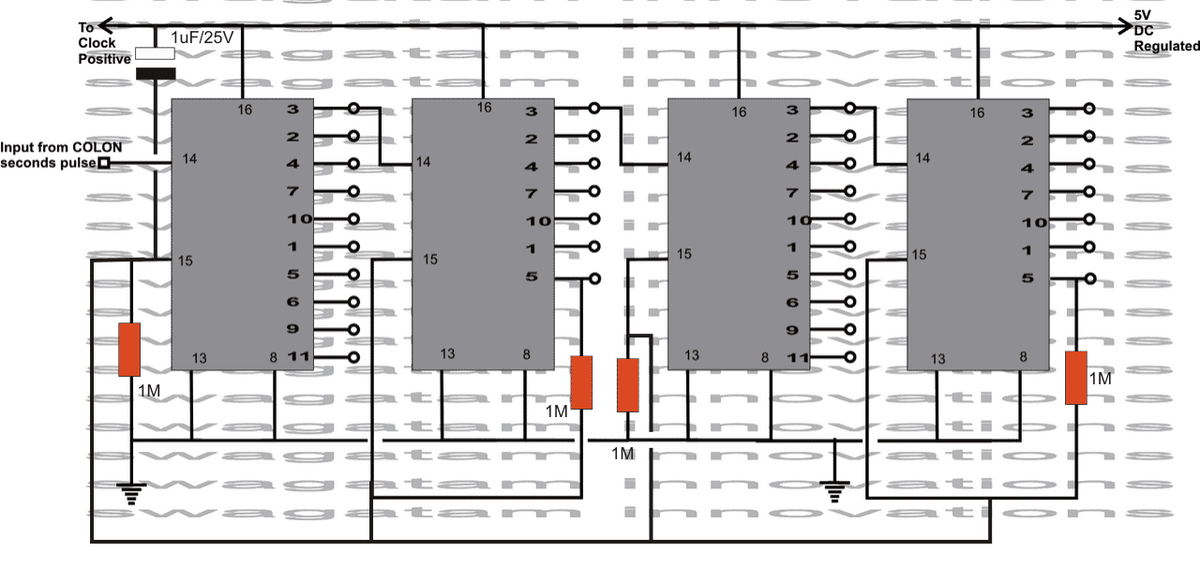

8237A funciona en dos cicles: cicle ideal i cicle actiu, on cada cicle conté 7 estats separats compostos per un període de rellotge cadascun.

S0- El primer estat, on el controlador ha sol·licitat el bus i espera l’acceptació del processador.

S1, S2, S3, S4 s’anomenen estats de treball del 8237A on té lloc la transferència real de dades. Si es necessita més temps per transferir els estats d'espera, s'afegeixen SW entre aquests estats.

Per a la transferència de memòria a memòria, cal fer transferències de lectura de memòria i escriptura a memòria. Es necessiten vuit estats per a la transferència única. Els primers quatre estats amb els índexs S11, S12, S13, S14 fan la transferència de lectura de memòria i els quatre següents S21, S22, S23, S24 són per a la transferència d’escriptura a memòria.

DMA passa a l'estat ideal quan cap canal sol·licita servei i realitza l'estat SI. SI és un estat inactiu on el DMA està inactiu fins que rep una sol·licitud. En aquest estat, DMA es troba en condicions de programa on el processador pot programar el DMA.

Quan DMA es troba en l’estat ideal i no rep més sol·licituds de canal, emet un senyal HRQ al processador i entra en estat actiu on pot iniciar la transferència de dades ja sigui en mode ràfega, en mode de robatori de cicle o en mode transparent.

8237 Diagrama de pins

Controlador DMA 8257

Quan es combina amb un dispositiu de port d'E / S Intel 8212, el controlador DMA 8257 forma un canal complet de 4 canals Controlador DMA . En rebre una sol·licitud de transferència, el controlador 8257-

- Adquireix el control sobre el bus del sistema del processador.

- Es reconeix el perifèric connectat al canal de màxima prioritat.

- Els bits menys significatius de l'adreça de memòria es mouen sobre les línies d'adreces A0-A7 del bus del sistema.

- El més significatiu 8 bits de l'adreça de memòria es condueixen al port d'E / S 8212 mitjançant línies de dades.

- Genera els senyals de control adequats per a la transferència de dades entre perifèrics i ubicacions de memòria adreçades.

- Quan es transfereix el nombre especificat de bytes, el controlador informa el final de la transferència de la CPU activant la sortida de recompte de terminals (TC).

Per a cada canal 8257 conté dos Registres de 16 bits - 1) Registre d’adreces DMA i 2) Registre de recompte de terminals, que s’hauria d’inicialitzar abans d’habilitar un canal. L'adreça de la primera ubicació de memòria a la qual s'accedeix es carrega al registre d'adreces DMA. L'ordre inferior de 14 bits del valor carregat al registre de recompte de terminals indica el nombre de cicles DMA menys un abans de l'activació de la sortida de recompte de terminals. El tipus d’operació d’un canal s’indica amb els dos bits més significatius del registre de recompte de terminals.

8257 Diagrama de pins

Avantatges i desavantatges del controlador DMA

Els avantatges i desavantatges del controlador DMA inclouen els següents.

Avantatges

- DMA accelera les operacions de memòria ignorant la participació de la CPU.

- La sobrecàrrega de treball a la CPU disminueix.

- Per a cada transferència, només calen uns quants cicles de rellotge

Desavantatges

- El problema de coherència de la memòria cau es pot veure quan s’utilitza DMA per a la transferència de dades.

- Augmenta el preu del sistema.

DMA ( Accés directe a la memòria ) El controlador s’utilitza en targetes gràfiques, targetes de xarxa, targetes de so, etc. El DMA també s’utilitza per a la transferència intra-xip en processadors multi-core. Funcionant en un dels seus tres modes, DMA pot reduir considerablement la càrrega del processador. Amb quin dels modes de DMA heu treballat? Quin dels modes que considereu és més eficaç?