JTAG (Joint Test Action Group) és un estàndard IEEE 1149.1 ben establert que es va desenvolupar l'any 1980 per resoldre els problemes de fabricació que es van produir a les plaques electròniques o plaques de circuit imprès . Aquesta tecnologia s'utilitza per proporcionar prou accés de prova per a cada tauler complex quan l'accés de prova estava disminuint. Així, es va llançar la tecnologia d'escaneig de límits i l'estàndard JTAG o Especificació JTAG està establert. La complexitat de l'electrònica ha anat augmentant dia a dia, de manera que l'especificació JTAG s'ha convertit en el format de prova acceptat per provar unitats electròniques complicades i compactes. Aquest article tracta una visió general d'a JTAG protocol: treball amb aplicacions.

Què és JTAG?

El nom que es dóna al port d'accés de prova estàndard IEEE 1149.1 així com a l'arquitectura Boundary-Scan es coneix com a JTAG (Joint Test Action Group). Aquesta arquitectura d'exploració de límits s'utilitza principalment a l'ordinador processadors perquè el primer processador amb JTAG va ser llançat per Intel. Aquest estàndard IEEE simplement defineix com es prova el circuit d'un ordinador per confirmar si funciona correctament després del procediment de fabricació. A les plaques de circuit, es realitzen proves per comprovar les juntes de soldadura.

Joint Test Action Group ofereix una visió de pins per als provadors amb cada coixinet IC que ajuda a identificar qualsevol fallada dins d'una placa de circuit. Una vegada que aquest protocol està connectat a un xip, aquest pot connectar una sonda al xip permetent que un desenvolupador controli el xip així com les seves connexions amb altres xips. Els desenvolupadors també poden utilitzar la interfície amb el grup d'acció de prova conjunta per copiar el microprogramari a la memòria no volàtil d'un dispositiu electrònic.

Configuració/Pin Out

El Joint Test Action Group inclou 20 pins on es comenten cada pin i la seva funció a continuació.

Pin1 (VTref): Aquest és el pin de tensió de referència de l'objectiu que s'utilitza per connectar-se a la font d'alimentació principal de l'objectiu que oscil·la entre 1,5 i 5,0 VDC.

Pin2 (Vsupply): Aquesta és la tensió d'alimentació objectiu que s'utilitza per connectar l'alimentació de tensió principal de l'objectiu 1.5VDC - 5.0VDC.

Pin3 (nTRST): Aquest és un pin de restabliment de prova que s'utilitza per restablir la màquina d'estat del controlador TAP.

Pins (4, 6, 8, 10, 12, 14, 16, 18 i 20): Aquests són pins GND comuns.

Pin5 (TDI): Aquestes són les dades de prova al pin. Aquestes dades es traslladen al dispositiu de destinació. Aquest pin s'ha de tirar cap amunt en una condició definida al tauler objectiu.

Pin7 (TMS): Aquest és el pin d'estat del mode de prova que s'extreu per determinar la següent condició de la màquina d'estat del controlador TAP.

Pin9 (TCK): Aquest és un pin de rellotge de prova que sincronitza les operacions internes de la màquina d'estat al controlador TAP.

Pin11 (RTCK): Aquest és el pin TCK de retorn d'entrada que s'utilitza en dispositius que admeten el rellotge adaptatiu.

Pin13 (TDO): Aquest és el pin de sortida de dades de prova, de manera que les dades es mouen fora del dispositiu objectiu cap a Flyswatter.

Pin15 (nSRST): Aquest és el pin de restabliment del sistema objectiu que està connectat al senyal de restabliment principal de l'objectiu.

Pins 17 i 19 (NC): Aquests no són pins connectats.

JTAG funcionant

L'ús original del JTAG és per a proves de límits. Aquí hi ha una placa de circuit imprès senzilla que inclou dos circuits integrats com CPU i FPGA . Una placa típica pot incloure molts IC. En general, els circuits integrats inclouen molts pins connectats conjuntament amb moltes connexions. Aquí, al diagrama següent, només es mostren quatre connexions.

Així que si dissenyeu moltes plaques on cada placa tingui milers de connexions. En això, hi ha alguns taulers dolents. Per tant, hem de comprovar quina placa funciona i quina no. Per això, es va dissenyar el Joint Test Action Group.

Aquest protocol pot utilitzar els pins de control de tots els xips, però al diagrama següent, el Joint Test Action Group farà tots els pins de sortida de la CPU i tots els pins d'entrada de FPGA. Després d'això, en transmetre una quantitat de dades dels pins de la CPU i llegir els valors dels pins de la FPGA, JTAG afirma que les connexions de la placa PCB estan bé.

De fet, el Joint Test Action Group inclou quatre senyals lògics TDI, TDO, TMS i TCK. I aquests senyals s'han de connectar d'una manera particular. Al principi, TMS i TCK estan connectats en paral·lel a tots els circuits integrats de JTAG.

Després d'això, tant el TDI com el TDO estan connectats per formar una cadena. Com podeu observar, cada IC compatible amb JTAG inclou 4 pins que s'utilitzen per a JTAG on 3 pins són entrades i el quart pin surt. El cinquè pin com TRST és opcional. Normalment, els pins JTAG no es comparteixen amb altres finalitats.

Mitjançant l'ús del Joint Test Action Group, tots els IC utilitzen proves de límits que el motiu original és creat per JTAG. En l'actualitat, l'ús d'aquest protocol s'ha estès per permetre diferents coses, com ara configurar FPGA i després, JTAG s'utilitza al nucli FPGA amb finalitats de depuració.

Arquitectura JTAG

L'arquitectura JTAG es mostra a continuació. En aquesta arquitectura, tots els senyals entre la lògica bàsica del dispositiu i els pins s'interrompen mitjançant un camí d'exploració en sèrie anomenat BSR o Boundary Scan Register. Aquest BSR inclou diverses 'cel·les' d'exploració de límits. En general, aquestes cel·les d'exploració de límits no són visibles, però es poden utilitzar per establir o llegir valors dins del mode de prova des dels pins del dispositiu.

La interfície JTAG anomenada TAP o port d'accés de prova utilitza diferents senyals per donar suport a l'operació d'exploració de límits com TCK, TMS, TDI, TDO i TRST.

- El senyal TCK o Test Clock simplement sincronitza les operacions interiors d'una màquina d'estat.

- El senyal TMS o de selecció de mode de prova es mostra a la vora creixent d'un senyal de rellotge de prova per decidir el següent estat.

- El senyal TDI o Test Data In significa les dades desplaçades al dispositiu de prova, en cas contrari, la lògica de programació. Una vegada que la màquina d'estat interior està en l'estat correcte, es mostra a la vora creixent de TCK.

- TDO o senyal de sortida de dades de prova significa les dades desplaçades cap a fora del dispositiu de prova, en cas contrari, la lògica de programació. Una vegada que la màquina d'estat interior està en l'estat correcte, és vàlida a la vora decreixent de TCK

- TRST o Test Reset és un pin opcional que s'utilitza per restablir la màquina d'estat del controlador TAP.

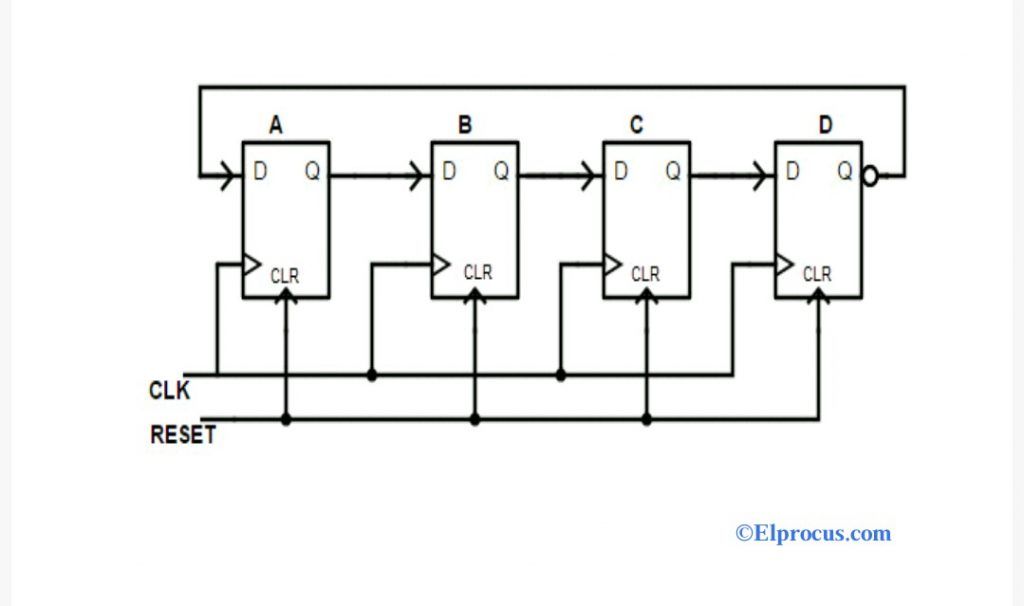

Controlador TAP

El punt d'accés de prova a l'arquitectura de JTAG es compon d'un controlador TAP, un registre d'instruccions i registres de dades de prova. Aquest controlador inclou la màquina d'estat de prova que és responsable de llegir els senyals TMS i TCK. Aquí, el pin i/p de dades s'utilitza simplement per carregar dades a les cel·les de límit entre el nucli IC i els pins físics, i també carregar dades en un dels registres de dades o al registre d'instruccions. El pin de dades o/p s'utilitza per llegir dades dels registres o de les cel·les de límit.

La màquina d'estats del controlador TAP està controlada pel TMS i està registrada per TCK. La màquina d'estat utilitza dos camins per significar dos modes diferents, com ara el mode d'instrucció i el mode de dades.

Registres

Hi ha dos tipus de registres disponibles dins de l'exploració de límits. Cada dispositiu compatible inclou com a mínim dos registres de dades o més i un registre d'instruccions.

Registre d'instruccions

El registre d'instruccions s'utilitza per contenir la instrucció actual. Així, les seves dades són utilitzades pel controlador TAP per decidir què executar amb els senyals que s'obtenen. Amb més freqüència, les dades del registre d'instruccions descriuen a quin dels registres de dades s'han de passar els senyals.

Registres de dades

Els registres de dades estan disponibles en tres tipus: el registre BSR (Registre d'escaneig de límits), el registre BYPASS i el registre ID CODES. A més, hi poden haver altres registres de dades, però no són necessaris com a element de l'estàndard JTAG.

Registre d'exploració de límits (BSR)

BSR és el registre de dades de prova principal que s'utilitza per desplaçar les dades des i cap als pins d'E/S del dispositiu.

BYPASS

El bypass és un registre d'un sol bit utilitzat per passar dades de TDI - TDO. Per tant, permet provar dispositius addicionals dins d'un circuit amb una sobrecàrrega mínima.

CODIS ID

Aquest tipus de registre de dades inclou el codi d'identificació i el número de revisió del dispositiu. Així, aquestes dades permeten connectar el dispositiu al seu fitxer BSDL (Boundary Scan Description Language). Aquest fitxer incloïa els detalls de configuració de Boundary Scan per al dispositiu.

El funcionament de JTAG és, inicialment, el mode d'instrucció s'escull on un dels estats d'aquest mode 'camí' permet que l'operador rellotge dins d'una instrucció de TDI. Després d'això, la màquina de l'estat es desenvolupa fins que es reorganitza. El següent pas per a la majoria de les instruccions és triar el mode de dades. Així, en aquest mode, les dades es carreguen mitjançant TDI per llegir-les des de TDO. Per a TDI i TDO, els camins de dades s'ordenaran d'acord amb la instrucció que s'ha registrat. Un cop feta l'operació de lectura/escriptura, la màquina d'estat torna a desenvolupar-se a l'estat de reinici.

Diferència entre JTAG i UART

La diferència entre JTAG i UART inclou el següent.

| JTAG |

UART |

| El terme 'JTAG' significa Joint Test Action Group. | El terme ' UART ” són les sigles de Receptor/Transmissor asíncron universal. |

| És una interfície síncrona que utilitza maquinari integrat per programar el flaix . | UART és una interfície asíncrona que utilitza un carregador d'arrencada que s'executa dins de la memòria. |

| És un conjunt de ports de prova que s'utilitzen per a la depuració, però també es poden utilitzar per programar firmware (que es fa habitualment).

|

L'UART és un tipus de xip que controla les comunicacions cap a i des d'un dispositiu, com ara un microcontrolador, ROM, RAM, etc. La majoria de vegades, és una connexió en sèrie que ens permet comunicar-nos amb un dispositiu. |

| Aquests estan disponibles en quatre tipus TDI, TDO, TCK, TMS i TRST. | Aquests estan disponibles en dos tipus UART mudes i FIFO UART. |

| Joint Test Action Group és un protocol de programació en sèrie o d'accés a dades que s'utilitza en la interfície de microcontroladors i dispositius relacionats. | Un UART és un tipus de xip, d'altra manera, el subcomponent del microcontrolador que s'utilitza per proporcionar el maquinari per generar un flux sèrie asíncron com RS-232/RS-485. |

| Els components JTAG són processadors, FPGA, CPLD , etc. | Els components UART són el generador CLK, registres de desplaçament d'E/S, búfers de transmissió o recepció, búfer de bus de dades del sistema, lògica de control de lectura o escriptura, etc. |

Analitzador de protocols JTAG

L'analitzador de protocols JTAG com PGY-JTAG-EX-PD és un tipus d'analitzador de protocols que inclou algunes funcions per capturar i depurar la comunicació entre l'amfitrió i el disseny en prova. Aquest tipus d'analitzador és l'instrument líder que permet als enginyers de prova i disseny provar els dissenys particulars de JTAG per a les seves especificacions mitjançant l'organització del PGY-JTAG-EX-PD com a mestre o esclau per generar trànsit JTAG i descodificar els paquets de descodificació del Protocol del grup d'acció de prova conjunta.

Característiques

Les característiques de l'analitzador de protocols JTAG inclouen les següents.

- Admet fins a 25MH de freqüències JTAG.

- Genera trànsit JTAG i descodificació de protocols per al bus simultàniament.

- Té capacitat JTAG Master.

- Velocitats variables de dades JTAG i cicle de treball.

- Retards TDI i TCK definits per l'usuari.

- Interfície USB 2.0 o 3.0 de l'ordinador host.

- Anàlisi d'errors dins de Protocol Decode

- Diagrama de temps del bus descodificat del protocol.

- Transmissió contínua de dades de protocol a l'ordinador amfitrió per proporcionar un buffer gran.

- Llista d'activitats del protocol.

- A diverses velocitats, es pot escriure un script d'exercici per combinar la generació de marcs de dades múltiples.

Diagrama de temps

El diagrama de temps del JTAG el protocol es mostra a continuació. Al diagrama següent, el pin TDO es manté dins de la condició d'alta impedància, excepte durant un estat del controlador shift-IR/shift-DR.

En les condicions del controlador shift-IR i Shift-DR, el pin TDO s'actualitza a la vora decreixent de TCK a través de Target i es mostra a la vora creixent de TCK a través de l'amfitrió.

Tant els pins TDI com TMS es mostren simplement a la vora creixent de TCK a través de Target. Actualitzat a la vora decreixent, en cas contrari, TCK a través de l'amfitrió.

Aplicacions

El Aplicacions JTAG incloure el següent.

- Joint Test Action Group s'utilitza amb freqüència als processadors per proporcionar el dret d'entrada a les seves funcions d'emulació o depuració.

- Tots els CPLD i FPGA utilitzen això com a interfície per donar accés a les seves funcions de programació.

- S'utilitza per a proves de PCB sense accés físic

- S'utilitza per a proves de fabricació a nivell de placa.

Per tant, tot això es tracta una visió general de JTAG – configuració de pins, treballant amb aplicacions. L'estàndard de la indústria JTAG s'utilitza per a la verificació del disseny, així com per a les proves de PCB després de la fabricació. Aquí hi ha una pregunta per a vostè, JTAG significa?