Programari de simulació

La simulació és el procés de dissenyar un model d’un sistema real i realitzar experiments amb un model amb el propòsit de comprendre el comportament del sistema o avaluar diversos passos per aconseguir el funcionament del sistema.

El fet de simular alguna cosa primer requereix que es desenvolupi un model que representi els comportaments / funcions del sistema físic seleccionat.

La simulació s'utilitza en molts contextos, per exemple, la simulació de tecnologia per a l'optimització del rendiment, proves, formació i educació. I sovint s’utilitzen experiments per ordinador per estudiar models de simulació. El procés de simulació s’utilitza per provar el circuit que es dissenya permanentment perquè el canvi de maquinari és molt difícil quan el circuit no funciona correctament.

La simulació és un procés de prova del disseny aplicant entrades a un circuit i veient o observant el seu comportament. La sortida d’una simulació és un conjunt de formes d’ona que mostren com es comporta un circuit sobre una seqüència determinada d’entrades.

En general, la simulació és de dos tipus: simulació funcional i simulació de temps. La simulació funcional prova el funcionament lògic d'un circuit sense explicar diferències en el circuit. La simulació funcional és ràpida i útil per comprovar l’efecte principal del circuit dissenyat.

La simulació de temps és més assenyada que la simulació funcional. En aquest procés de simulació, els components lògics i els cables fan un pas enrere per reaccionar a l'entrada. I per provar el funcionament lògic del circuit, indica la sincronització dels senyals del circuit i es necessita més temps per realitzar-la.

Hi ha moltes tècniques de simulació per provar circuits, en aquest article veurem sobre una simulació mitjançant PROTEUS.

PROTEUS és un dels programes de disseny de PCB més famosos. S'integra amb la capacitat de simulació i simulació bàsica SPICE per crear un sistema complet de disseny electrònic. Redueix el temps de desenvolupament en comparació amb altres processos de disseny incrustats. Vegem un exemple amb el programari PROTEUS per a la simulació.

Els següents passos estan implicats en el procés de simulació mitjançant PROTEUS:

PAS 1: Al pas 1, seleccioneu el dispositiu a la barra de visualització escrivint el nom del dispositiu (per exemple: portes lògiques, commutadors i dispositius electrònics bàsics).

PAS 2: Col·locació dels components.

PAS 3: Lloc<>a la zona de dibuix i feu clic amb el botó dret a la resistència i seleccioneu<>

PAS 4: Referència del component: s'assigna automàticament

Valor del component: Editable

PAS 5: Selecció de fonts

PAS 6: Col·loqueu la font de tensió (VSOURCE) a la zona de dibuix. A continuació, feu clic amb el botó dret a VSOURCE, seleccioneu<>llavors<>

PAS 7: Connexió de cable, feu clic a l’encaminador automàtic de cable i connecteu el terminal de components segons la topologia.

PAS 8: Afegir terminal / terra: feu clic a<>, Seleccioneu<>i lloc<>a la zona de dibuix.

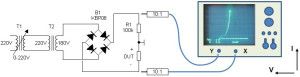

PAS 9: La sortida podria ser el voltatge / corrent de qualsevol element del circuit. Les mesures a PROTEUS són principalment les sondes de tensió / corrent. La sonda actual hauria de ser al fil horitzontal.

Hi ha dos tipus de simulacions: Simulació interactiva: s’utilitza principalment per a senyals digitals. Simulació basada en gràfics: s'utilitza principalment per a senyals analògics.

PAS 10: Fer clic a<>, seleccioneu<>a continuació, col·loqueu la finestra del gràfic a l'àrea de dibuix<>.

PAS 11 :

<>hora d’inici / aturada

<>

- Es trien formes d'ona de sonda ja col·locades

- Diferents<>es podria seleccionar l’escala de l’eix y

Després comença<>

La sonda de tensió mesura la tensió del node on es col·loca. Per trobar una tensió de l’element, s’haurien de subestructurar les tensions del node terminal de l’element. Aquesta operació es podria fer.

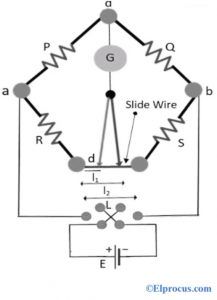

Representació esquemàtica de la simulació:

El diagrama de blocs esquemàtic anterior es classifica en dues parts anomenades estudi del món real i simulació. El sistema en estudi i l’alteració del sistema pertanyen al món real i l’estudi del sistema significa que el sistema prova el disseny del maquinari simulat aplicant entrades a un circuit i observant el seu rendiment. A l’altra banda, es col·loca el model de simulació per modelar l’experiment simulat i, després de l’experiment del model de simulació, analitza l’operació completa.

El diagrama de blocs esquemàtic anterior es classifica en dues parts anomenades estudi del món real i simulació. El sistema en estudi i l’alteració del sistema pertanyen al món real i l’estudi del sistema significa que el sistema prova el disseny del maquinari simulat aplicant entrades a un circuit i observant el seu rendiment. A l’altra banda, es col·loca el model de simulació per modelar l’experiment simulat i, després de l’experiment del model de simulació, analitza l’operació completa.

Avantatges de la simulació:

- Dóna la idea i la implementació adequades del nostre codi i circuit abans d'implementar el maquinari.

- La configuració del model de sistema és tan senzilla.

- El procés de simulació és segur de manejar.

- El procés de simulació s’utilitza principalment per conèixer el rendiment del sistema

- Sense entrar en la construcció del sistema podem estudiar el comportament del sistema.

- El modelatge, el disseny i altres àrees del sistema de dispositius de maquinari nous poden realitzar l'operació de prova sense comprometre el recurs per aconseguir-ho.

- Redueix el temps en crear maquinari i provar els vostres errors directament en maquinari. Podeu analitzar el circuit i el codi a Proteus i trobar els errors que es produeixen abans d'implementar-lo al maquinari.

Inconvenients de la simulació:

- Aquest procés és difícil de depurar.

- Aquest procés és força rendible.

- No podem introduir un número exacte.

Programari de codificació incrustat

Programari KEIL:

Això El programari és un entorn de desenvolupament integrat que us ajuda a escriure, compilar i depurar programes incrustats. El programari Keil s’utilitza per escriure un llenguatge de nivell de muntatge. Els podem descarregar des dels seus llocs web. Tot i això, la mida del codi per a aquestes versions de shareware és limitada i hem de considerar quin muntador és adequat per a la nostra aplicació.

Encapsula els components següents:

- Un cap de projecte

- Una instal·lació de marca

- Configuració de l'eina

- editor

- Un depurador potent

- Per crear (compilar, muntar i enllaçar) una aplicació a uVision2, heu de:

- Seleccioneu Projecte – Obre projecte (per exemple, C166 EXAMPLES HELLO HELLO.UV2 )

- Seleccioneu Projecte: Reconstrueix tots els fitxers de destinació o Crea destinació. UVision2 compila, reuneix i enllaça els fitxers del vostre projecte.

- Creació de l'aplicació pròpia:

- Per crear un projecte nou, heu de:

- Seleccioneu Projecte - Projecte nou.

- Seleccioneu un directori i introduïu el nom del fitxer del projecte.

- Selecciona projecte: seleccioneu dispositiu i seleccioneu un dispositiu 8051, 251 o C16x / ST10 al dispositiu

- Base de dades

- Creeu fitxers font per afegir-los al projecte.

- Seleccioneu Projecte: objectius, grups i fitxers. Afegeix / Fitxers, seleccioneu Font de grup1 i afegiu els fitxers font al projecte.

- Seleccioneu Projecte - Opcions i configureu les opcions de l'eina. Tingueu en compte que quan seleccioneu el dispositiu de destinació a la base de dades de dispositius, totes les opcions especials s'estableixen automàticament. Només cal configurar el mapa de memòria del maquinari de destinació. La configuració predeterminada del model de memòria és òptima per a la majoria.

Aplicacions:

- Seleccioneu Projecte: Reconstrueix tots els fitxers de destinació o Crea destinació.

Depurar una aplicació:

Per depurar una aplicació creada, heu de:

- Seleccioneu Depuració - Inicia / Atura la sessió de depuració.

- Utilitzeu els botons de la barra d'eines Step per fer un sol pas pel programa. Podeu introduir G, main a la finestra de sortida per executar a la funció C. principal.

- Obriu la finestra de sèrie mitjançant el botó de sèrie # 1 de la barra d'eines.

- Depuració del programa mitjançant opcions estàndard com Step, Go i Break, etc.

Limitacions del programari d'elevació:

Les limitacions següents s'apliquen a les versions d'avaluació de les cadenes d'eines C51, C251 o C166. Limitacions del programari d'avaluació C51:

- El compilador, el muntador, l'enllaçador i el depurador estan limitats a 2 Kbytes de codi objecte, però el codi font pot tenir qualsevol mida. Els programes que generen més de 2 Kbytes de codi objecte no compilaran, muntaran ni enllaçaran el codi d’inici generat que inclou LJMP’s i no es poden utilitzar en dispositius d’un sol xip que admetin menys de 2 Kbytes d’espai de programa com el Philips 750/751/752.

- El depurador admet fitxers de 2 Kbytes o menys.

- Els programes comencen a offset 0x0800 i no es poden programar en dispositius d’un sol xip .

- No hi ha suport de maquinari disponible per a diversos registres DPTR.

- No hi ha suport disponible per a biblioteques d'usuaris ni aritmètica de punt flotant.

Programari d'elevació:

- Enllaçador / localitzador de codis bancaris

- Gestor de biblioteques.

- RTX-51 Sistema operatiu petit en temps real

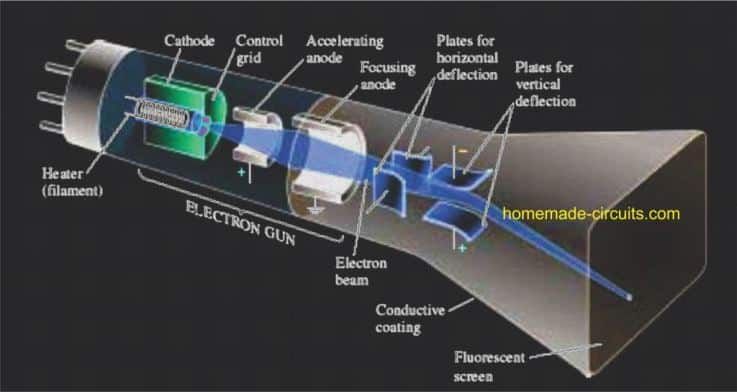

Simulació perifèrica:

El depurador Keil proporciona una simulació completa per a la CPU i els perifèrics integrats en xip de la majoria de dispositius incrustats. Per descobrir quins perifèrics d’un dispositiu són compatibles, a u vision2. Seleccioneu l'element Perifèrics simulats al menú Ajuda. També podeu utilitzar la base de dades de dispositius basada en web. Afegim constantment dispositius nous i suport de simulació per a perifèrics integrats en xip, així que assegureu-vos de consultar sovint la base de dades de dispositius.