Hi va haver una època en què els ordinadors tenien una mida tan enorme que per instal·lar-los es necessitava fàcilment un espai a l’habitació. Però avui estan tan evolucionats que fins i tot els podem portar fàcilment com a quaderns. La innovació que ho va fer possible va ser el concepte de circuits integrats. En Circuits integrats , un gran nombre d 'actius i elements passius juntament amb les seves interconnexions es desenvolupen sobre una petita hòstia de silici de 50 per 50 mils de secció transversal. Els processos bàsics seguits per a la producció d’aquests circuits inclouen el creixement epitaxial, la difusió de la impuresa emmascarada, el creixement d’òxids i el gravat d’òxids, mitjançant fotolitografia per fer patrons.

Els components de l’hòstia inclouen resistències, transistors, díodes, condensadors, etc. L’element més complicat de fabricar a través de circuits integrats són els transistors. Els transistors són de diversos tipus com CMOS, BJT, FET. Triem el tipus de tecnologia de transistors que s’implementarà a través d’un CI basat en els requisits. En aquest article ens familiaritzem amb el concepte de Fabricació CMOS (o) fabricació de transistors com CMOS.

Fabricació CMOS

Per a un menor requisit de dissipació d'energia Tecnologia CMOS s’utilitza per implementar transistors. Si necessitem un circuit més ràpid, els transistors s’implementaran IC utilitzant BJT . Fabricació de Transistors CMOS ja que els IC es poden fer en tres mètodes diferents.

La tecnologia N-well / P-well, on la difusió de tipus n es fa sobre un substrat de tipus p o la difusió de tipus p es fa sobre un substrat de tipus n respectivament.

El Tecnologia de dos bessons , on NMOS i transistor PMOS es desenvolupen sobre l’hòstia per difusió simultània sobre una base de creixement epitaxial, en lloc d’un substrat.

El procés Silici On Insulator, on en lloc d’utilitzar silici com a substrat s’utilitza un material aïllant per millorar la velocitat i la susceptibilitat de bloqueig.

Tecnologia N- well / P- well

El CMOS es pot obtenir integrant tots dos Transistors NMOS i PMOS sobre la mateixa hòstia de silici. En la tecnologia dels pous N, es difon un pou de tipus n sobre un substrat de tipus p, mentre que en el pou P és viceversa.

Passos de fabricació de CMOS

El Procés de fabricació de CMOS flux es realitza mitjançant vint passos bàsics de fabricació mentre es fabrica amb tecnologia N-well / P-well.

Elaboració de CMOS amb N bé

Pas 1: Primer, escollim un substrat com a base per a la fabricació. Per a N- well, se selecciona un substrat de silici tipus P.

Substrat

Pas 2: oxidació: La difusió selectiva d’impureses de tipus n s’aconsegueix utilitzant SiO2 com a barrera que protegeix parts de l’hòstia contra la contaminació del substrat. SiO2es distribueix mitjançant un procés d’oxidació exposat el substrat a oxigen i hidrogen d’alta qualitat en una cambra d’oxidació a aproximadament 1.0000c

Oxidació

Pas 3: Creixement del fotoresist: En aquesta etapa, per permetre el gravat selectiu, la capa de SiO2 se sotmet al procés de fotolitografia. En aquest procés, l’hòstia es recobreix amb una pel·lícula uniforme d’una emulsió fotosensible.

Creixement del fotoresist

Pas 4: emmascarament: Aquest pas és la continuació del procés de fotolitografia. En aquest pas, es fa un patró d'obertura desitjat mitjançant una plantilla. Aquesta plantilla s’utilitza com a màscara sobre la fotoresistència. Ara el substrat està exposat Raigs UV el fotoresist present a les regions exposades de la màscara es polimeritza.

Enmascarament del fotoresist

Pas 5: eliminació del fotoresist no exposat: S’elimina la màscara i es dissol la regió de fotoresistència no exposada desenvolupant una hòstia mitjançant un producte químic com el tricloroetilè.

Eliminació de Photoresist

Pas 6: gravat: L'hòstia es troba immersa en una solució de gravat d'àcid fluorhídric, que elimina l'òxid de les zones a través de les quals s'han de difondre els dopants.

Gravat de SiO2

Pas 7: eliminació de tota la capa de fotoresistència: Durant el procés de gravat , les porcions de SiO2 protegides per la capa de fotoresistència no es veuen afectades. Ara la màscara fotoresistent s’elimina amb un dissolvent químic (H2SO4 calent).

Eliminació de la capa de fotoresistència

Pas 8: formació del pou N: Les impureses de tipus n es difonen al substrat de tipus p a través de la regió exposada formant així un pou N.

Formació del pou N

Pas 9: eliminació de SiO2: Ara s’elimina la capa de SiO2 mitjançant l’ús d’àcid fluorhídric.

Eliminació de SiO2

Pas 10: deposició de polisilici: El desalineament de la porta d'un Transistor CMOS conduiria a la capacitat no desitjada que podria danyar el circuit. Per tant, per evitar aquest 'procés de porta autoalineada' es prefereix quan es formen regions de porta abans de la formació de la font i el drenatge mitjançant la implantació d'ions.

Diposició de polisilici

El polisilici s’utilitza per a la formació de la porta, ja que pot suportar temperatures elevades superiors a 80000c quan una hòstia se sotmet a mètodes de recuit per a la formació de la font i el drenatge. El polisilici es diposita utilitzant Procés de deposició química sobre una fina capa d'òxid de porta. Aquest prim òxid de porta sota la capa de polisilici evita el dopatge posterior a la regió de la porta.

Pas 11: formació de la regió Gate: Excepte les dues regions necessàries per a la formació de la porta per a Transistors NMOS i PMOS la porció restant de polisilici es treu.

Formació de la regió de la porta

Pas 12: procés d'oxidació: Una capa d'oxidació es diposita sobre la hòstia que actua com a escut per a més processos de difusió i metal·lització .

Procés d’oxidació

Pas 13: emmascarament i difusió: Per fer regions per a la difusió d’impureses de tipus n mitjançant el procés d’emmascarament es produeixen petits buits.

Enmascarament

Mitjançant el procés de difusió es desenvolupen tres regions n + per a la formació de terminals de NMOS.

Difusió de N

Pas 14: eliminació d'òxid: La capa d’òxid s’elimina.

Eliminació d’òxid

Pas 15: difusió tipus P: Semblant a la difusió de tipus n per formar els terminals de difusió de tipus p de PMOS.

Difusió tipus P

Pas 16 - Col·locació d'òxid de camp gruixut: Abans de formar els terminals metàl·lics es posa un òxid de camp espès per formar una capa protectora per a les regions de l'hòstia on no es requereixen terminals.

Capa d'òxid de camp gruixut

Pas 17: metal·lització: Aquest pas s'utilitza per a la formació de terminals metàl·lics que poden proporcionar interconnexions. L’alumini s’estén sobre tota l’hòstia.

Metal·lització

Pas 18 - Eliminació de l'excés de metall: L’excés de metall s’elimina de l’hòstia.

Pas 19: formació de terminals: En els buits formats després de l'eliminació de l'excés de metall es formen terminals per a les interconnexions.

Formació de terminals

Pas 20: assignació dels noms dels terminals: Els noms s’assignen als terminals de Transistors NMOS i PMOS .

Assignació de noms de terminals

Fabricació de CMOS mitjançant la tecnologia P well

El procés de pous p és similar al procés de pous N, tret que aquí s’utilitza substrat de tipus n i es duen a terme difusions de tipus p. Per simplicitat, en general, es prefereix el procés de N pous.

Fabricació de dos tubs de CMOS

Mitjançant el procés Twin-tube es pot controlar el guany dels dispositius tipus P i N. Diversos passos relacionats amb el fabricació de CMOS mitjançant el mètode Twin-tube són els següents

- Es pren un substrat de tipus n o p lleugerament dopat i s’utilitza la capa epitaxial. La capa epitaxial protegeix el problema de bloqueig del xip.

- Es conreen les capes de silici d'alta puresa amb gruix mesurat i concentració exacta de dopant.

- Formació de tubs per al pou P i N.

- Construcció d’òxid prim per protegir-se de la contaminació durant els processos de difusió.

- La font i el drenatge es formen mitjançant mètodes d’implantació d’ions.

- Es fan retallades per fer porcions de contactes metàl·lics.

- La metal·lització es realitza per dibuixar contactes metàl·lics

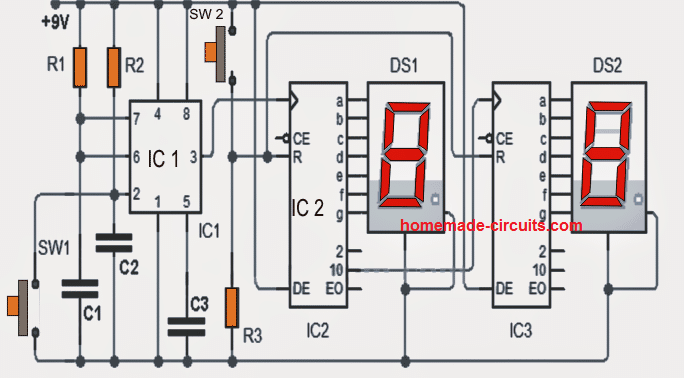

Disseny IC CMOS

La vista superior de a CMOS fabricació i disposició és donat. Aquí es poden veure clarament diversos contactes metàl·lics i difusions de N.

Disseny IC CMOS

Per tant, tot això es tracta Tècniques de fabricació de CMOS . Considerem una hòstia d'1 en quadrat dividida en 400 fitxes de superfície de 50 mil per 50 mil. Es necessita una superfície de 50 mil2 per fabricar un transistor. Per tant, cada CI conté 2 transistors, per tant hi ha 2 x 400 = 800 transistors construïts a cada hòstia. Si es processen 10 hòsties per lot, es poden fabricar 8000 transistors simultàniament. Quins són els diversos components que heu observat en un CI?