El missatge explica un circuit que apagarà un grup de làmpades en seqüència amb un ritme de retard predeterminat, tal com estableix l’usuari a través d’un pot integrat. Les idees les va demanar el senyor Azam Jamal

Especificacions tècniques

Vull fer un circuit que funcioni com: tinc bombetes CFL de 9 nos de 25 watts i vull que quan apague la primera bombeta, després de cada 5 minuts, la llum restant s'apagui regularment, de manera que cadascuna s'apagui després de 5 minuts d'altres significa que en 45 minuts s'apagaran els 9 llums respectivament.

Si us plau ajuda'm ?

El disseny

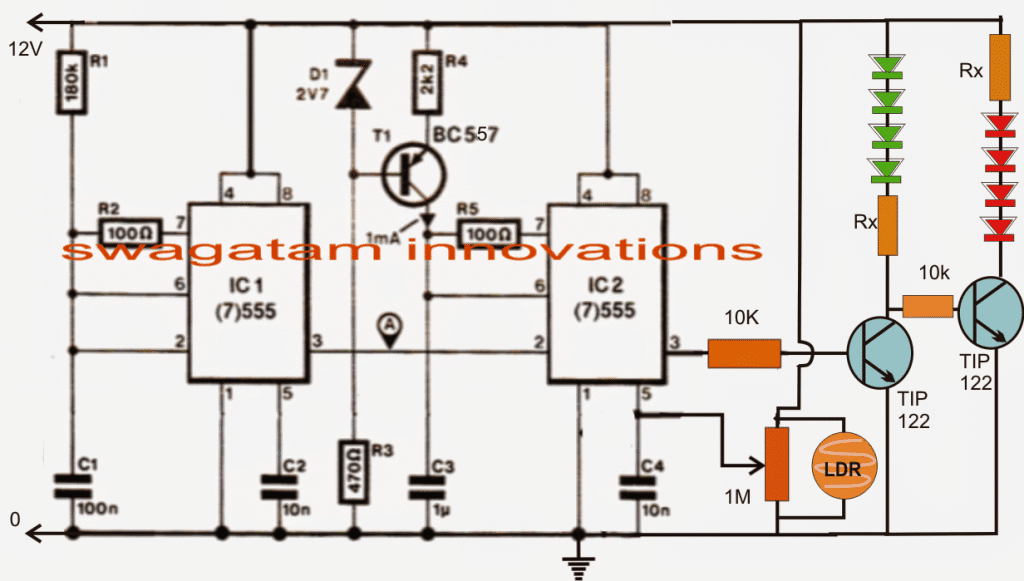

El funcionament del circuit es pot entendre de la següent manera:

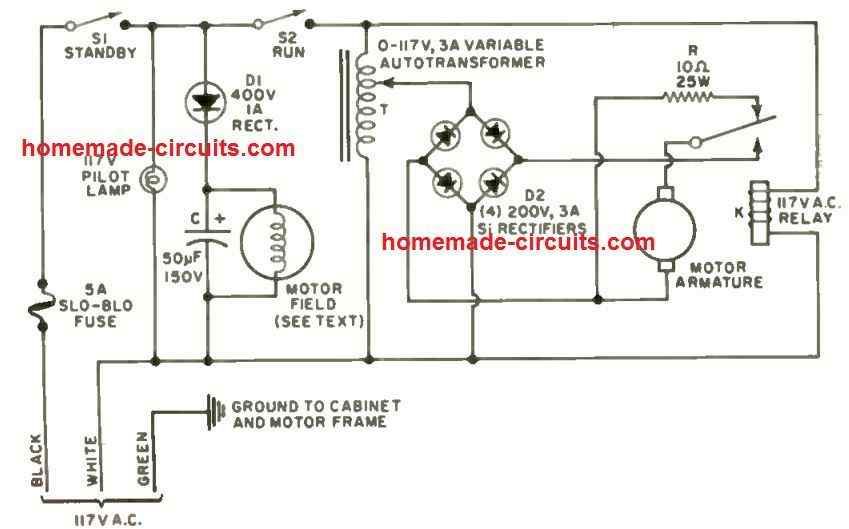

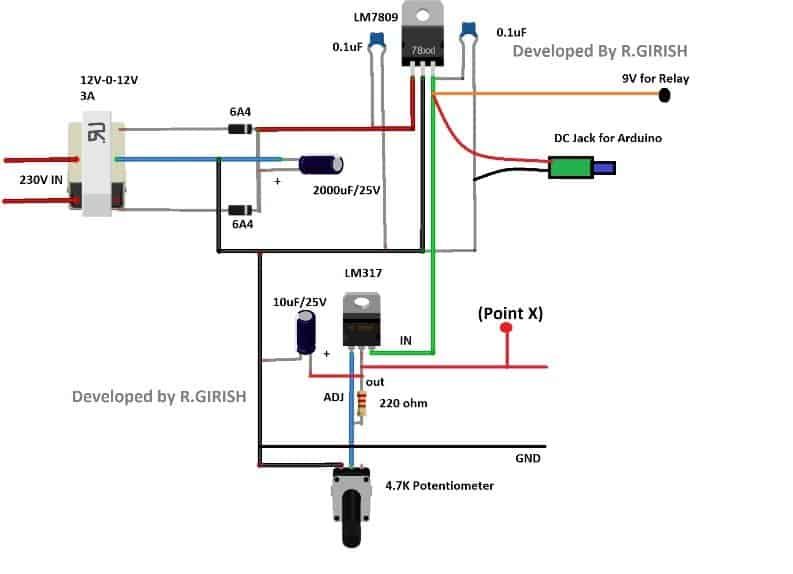

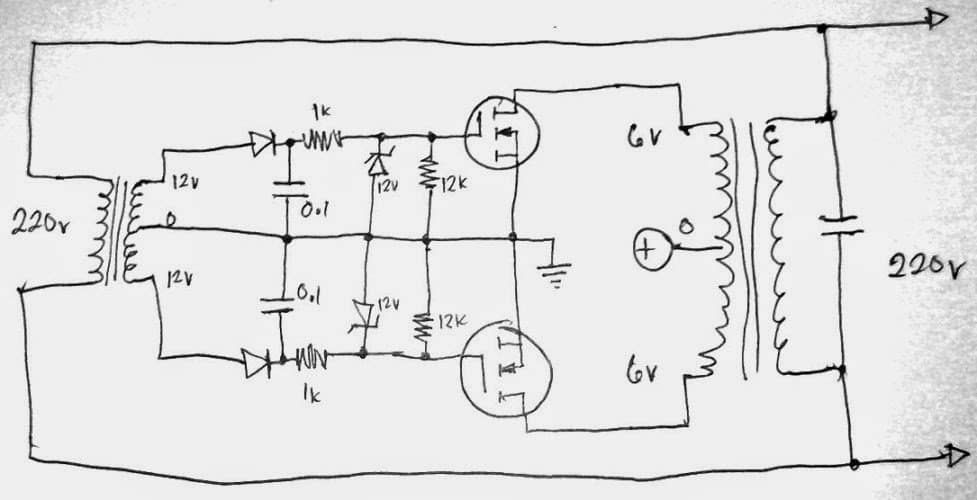

El primer circuit per sota del qual és un simple caçador de làmpades IC 555 i IC 4017 produeix la seqüenciació bàsica de les làmpades a un ritme de 5 minuts, la freqüència de temps està determinada per la configuració del pot de 100 k.

S'ha d'establir per produir una freqüència que pot ser del 50% de la velocitat de seqüenciació desitjada, és a dir, s'ha de configurar per produir els períodes ON i OFf a la velocitat de 2,5 minuts.

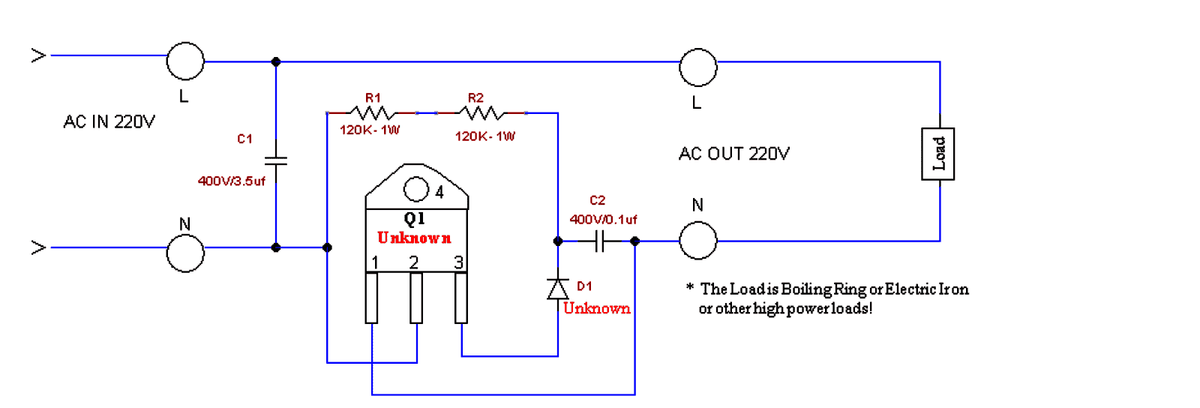

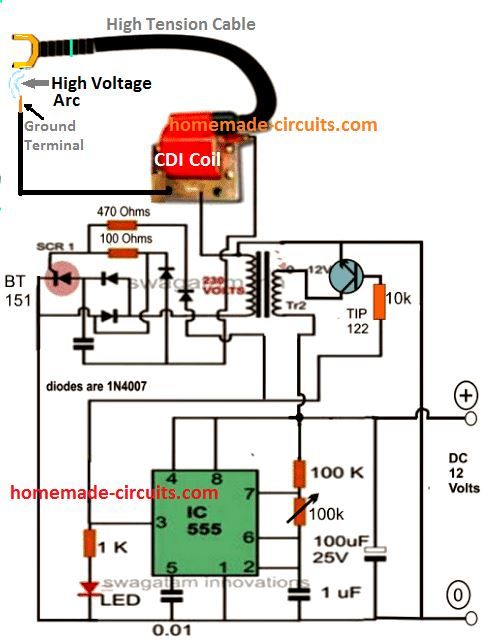

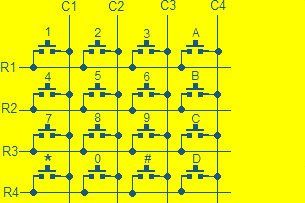

El segon circuit és un circuit de control de relés basat en SCR que s’ha de repetir 9 vegades a través de les sortides previstes del 4017 IC.

Segons la sol·licitud sempre que l'SPDT estigui alternat cap a la posició de terra, l'IC555 es manté desactivat i la primera làmpada (1) es manté encesa indefinidament.

També en aquesta posició, tots els pinouts de l'IC 4017 a partir del pin2 estan bloquejats a zero voltatge, el que significa que els controladors de relés SCR connectats tenen els seus relés a la seva posició N / C assegurant-se que totes les làmpades connectades romanen engegades.

Així, doncs, totes les nou làmpades del pin2 al pin11 de l’IC 4017 estan ara en una posició activada juntament amb el lamp1 associat a l’etapa de control del relé de transistors SPDT.

En el període desitjat quan es commuta l'SPDT, la primera làmpada (1) s'apaga i s'inicia el circuit de temporitzador 555 amb el seu procés de comptatge.

Al cap de 5 minuts, el 555 IC introdueix el seu primer impuls legítim al pin14 del 4017 fent que el pin2 passi a l'altura, que al seu torn bloqueja el controlador relé SCR rellevant apagant la primera làmpada de la seqüència.

Després de 5 minuts més, el pin4 passa a apagar el llum del controlador del relé SCR associat i el procés es repeteix fins que s'activa l'últim pin11 de la seqüència, apagant l'últim llum de la seqüència, i això també bloqueja el pin4 de l'IC555 congelant el conjunt fins que l'usuari restableixi les operacions per reiniciar el cicle de nou.

Esquema de connexions

L'etapa del conductor del relé

Anterior: S'han explicat 10 circuits senzills de transmissors de FM Següent: Circuit amplificador d’altaveus de classe D de 3,7 V per a entrada analògica diferencial