L'ECL (emissor coupled logic) va ser inventat per primera vegada a IBM l'agost de 1956 per Hannon S. Yourke. Aquesta lògica també es coneix com a lògica de mode actual, utilitzada als ordinadors d'IBM 7090 i 7094. La família ECL és molt ràpida en comparació amb lògica digital famílies. En general, aquesta família lògica proporciona un retard de propagació inferior a 1 ns. És una família lògica basada en transistors d'unió bipolar. És el circuit de la família lògica més ràpida accessible per dissenyar un sistema lògic convencional. Aquest article tracta una visió general d'un circuit lògic acoblat emissor , treballant amb aplicacions.

Què és la lògica acoblada d'emissors?

La lògica acoblada a l'emissor és la millor BJT Família lògica basada en el disseny de sistemes lògics convencionals. De vegades, també s'anomena lògica de mode actual, que és una tecnologia digital d'alta velocitat. En general, ECL es considera com l'IC lògic més ràpid on aconsegueix el seu funcionament d'alta velocitat utilitzant una variació de tensió molt petita i també evita que els transistors entrin a la regió de saturació.

Una implementació d'ECL utilitza una tensió d'alimentació positiva que es coneix com a PECL o ECL de referència positiva. A les primeres portes ECL, s'utilitza una font de tensió negativa a causa de la immunitat al soroll. Després d'això, l'ECL de referència positiva es va fer molt famós a causa dels seus nivells lògics més compatibles en comparació amb les famílies lògiques TTL.

La lògica acoblada a l'emissor dissipa una gran quantitat de potència estàtica, però, el seu consum global de corrent és baix en comparació amb CMOS a altes freqüències. Per tant, ECL és principalment beneficiós en circuits de distribució de rellotges i aplicacions basades en alta freqüència.

Característiques lògiques acoblades de l'emissor

Les característiques d'ECL els faran utilitzar en moltes aplicacions basades en alt rendiment.

- ECL proporciona dues sortides que es complementen sempre entre si perquè el funcionament del circuit es basa en un amplificador diferencial.

- Aquesta família lògica és adequada principalment per a mètodes de fabricació monolítics perquè els nivells lògics són una funció de les relacions de resistències.

- Els dispositius de la família ECL generen la sortida correcta i complementària de la funció proposada sense utilitzar cap inversor extern. En conseqüència, disminueix el nombre de paquets i els requisits d'energia i també disminueix els problemes que es produeixen per retards.

- Els dispositius ECL en disseny d'amplificador diferencial ofereixen una àmplia flexibilitat de rendiment, de manera que els circuits ECL permeten utilitzar-los tant com a circuits digitals com lineals.

- El disseny de la porta ECL té normalment una impedància d'entrada alta i baixa, la qual cosa és extremadament favorable per aconseguir un gran ventall i una capacitat d'accionament.

- Els dispositius ECL generen un drenatge de corrent constant a la font d'alimentació per simplificar el disseny de la font d'alimentació.

- Els dispositius d'ECL que inclouen sortides d'emissors oberts simplement els permeten incloure la capacitat d'accionament de la línia de transmissió.

Circuit lògic acoblat emissor

A continuació es mostra el circuit lògic acoblat a l'emissor per a l'inversor que està dissenyat amb resistències i transistors. En aquest circuit, els terminals emissors de dos transistors es connecten simplement a la resistència limitadora de corrent RE que s'utilitza per evitar que el transistor entri en saturació. Aquí la sortida del transistor es pren del terminal del col·lector en lloc del terminal de l'emissor. Aquest circuit proporciona dues sortides Vout (sortida inversora) i Vout2 (sortida no inversora) i el terminal d'entrada com Vin on es dóna una entrada alta o baixa. +Vcc = 5V.

Com funciona la lògica acoblada de l'emissor?

El funcionament de la lògica acoblada a l'emissor és que sempre que es doni l'entrada ALTA al circuit ECL, s'activarà el transistor 'Q1' i el transistor Q2 APAGAT, però el transistor Q1 no està saturat. Així, això farà que la sortida VOUT2 sigui ALTA i el valor de la sortida VOUT1 serà BAIX a causa de la caiguda dins de R1.

De la mateixa manera, quan el valor VIN donat a ECL és BAIX, s'apagarà el transistor Q1 i el transistor Q2 ON. Per tant, el transistor Q2 no passarà a la saturació. Per tant, farà que la sortida VOUT1 s'estiri ALTA i el valor de sortida VOUT2 serà baix a causa de la caiguda de la resistència R2.

Vegem com s'encén i s'apaga el transistor Q1 i Q2 quan s'aplica una tensió.

Els dos transistors com Q1 i Q2 d'aquest circuit estan connectats com a amplificador diferencial mitjançant una resistència emissora comú.

Els subministraments de tensió per a aquest circuit d'exemple són VCC = 5,0, VBB = 4,0 i VEE = 0 V. Els valors de nivell ALTA i BAIX d'entrada es defineixen simplement com a 4,4 V i 3,6 V. En realitat, aquest circuit genera nivells de sortida BAIX i ALTS que són 0,6 volts més alts; tanmateix, això es corregeix dins dels circuits ECL reals.

Una vegada que Vin és ALTA, el transistor Q1 s'activa, però no està saturat i el transistor Q2 s'apaga. Per tant, la tensió de sortida com VOUT2 s'eleva a 5 V a través de la resistència R2 i es pot demostrar que la caiguda de tensió a través de la resistència R1 és d'uns 0,8 V de manera que VOUT1 = 4,2 V (BAIX). A més VE = VOUT1 – VQ1 => 4,2 V – 0,4 V = 3,8 V ja que el transistor Q1 està completament encès.

Un cop Vin sigui BAIX, el transistor Q2 s'activarà, però no es saturat i el transistor Q1 s'apagarà. Per tant, VOUT1 es tira a 5,0 V mitjançant una resistència R1 i es pot demostrar que VOUT2 és de 4,2 V. També VE => VOUT2 – VQ2 => 4,2 V – 0,8 V => 3,4 V ja que el transistor Q2 està activat.

En ECL, els dos transistors mai estan en saturació com t Els canvis de tensió d'entrada/sortida són bastant petits com 0,8 v i la impedància d'entrada és alta i la resistència de sortida és baixa. Això ajuda l'ECL a funcionar més ràpid amb un temps de retard de propagació menor.

Circuit de porta OR/NOR acoblat amb emissors de dues entrades

A continuació es mostra el circuit de porta lògica OR/NOR acoblat amb dos emissors d'entrada. Aquest circuit està dissenyat modificant el circuit inversor anterior. La modificació és afegint un transistor addicional al costat d'entrada.

El funcionament d'aquest circuit és molt senzill. Quan les entrades aplicades als dos transistors Q1 i Q2 siguin baixes, la sortida 1 (Vout1) tindrà un valor ALTO. Per tant, aquest Vout1 correspon a la sortida de la porta NOR.

Simultàniament, si el transistor Q3 està encès, llavors farà que la segona sortida (Vout2) sigui ALTA. Per tant, aquesta sortida Vou2 correspon a la sortida de la porta OR.

De la mateixa manera, si les entrades dels transistors Q1 i Q2 són ALTES, encendrerà els transistors Q1 i Q2 i proporcionarà la sortida baixa al terminal VOUT1.

Si el transistor Q3 s'apaga durant aquesta operació, proporcionarà una sortida alta al terminal VOUT2. Per tant, a continuació es mostra la taula de veritat per a la porta OR/NOR.

|

Entrades |

Entrades | O |

NOR |

|

A |

B | I | I |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

Característiques lògiques acoblades a emissor

Les característiques d'ECL inclouen les següents.

- En comparació amb TTL, ECL té un temps de propagació més ràpid que oscil·la entre 0,5 i 2 ns. Però, la dissipació de potència lògica acoblada a l'emissor és més alta en comparació amb TTL com 30 mW.

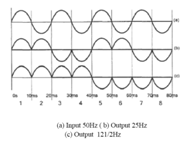

- Les tensions d'E/S d'ECL tenen un petit oscil·lació com 0,8.

- La impedància d'entrada de l'ECL és alta i la resistència de sortida és baixa; en conseqüència, el transistor canvia els seus estats molt ràpidament.

- La capacitat de sortida de l'ECL és alta i els retards de la porta són baixos.

- La lògica o/p d'ECL canvia d'un estat BAIX a un estat ALTO, però els nivells de tensió per a aquests estats variaran entre TTL i EC.

- La immunitat al soroll de l'ECL és de 0,4 V.

Avantatges i inconvenients

El avantatges de la lògica acoblada a emissor es comenten a continuació.

- El fanout d'ECL és de 25, millor que en comparació amb TTL i és baix en comparació amb CMOS.

- El temps mitjà de retard de propagació d'ECL és d'1 a 4 ns, que és millor en comparació amb CMOS i

- TTL. Per tant, s'anomena família lògica més ràpida.

- Quan els BJT a l'emissor es van acoblar portes lògiques treballen a la regió activa, llavors tenen la velocitat màxima en comparació amb totes les famílies lògiques.

- Les portes ECL generen sortides complementàries.

- Els pics de commutació actuals no hi ha als cables de la font d'alimentació.

- Les sortides es poden acoblar conjuntament per proporcionar la funció O per cable.

- Els paràmetres de l'ECL no canvien gaire a causa de la temperatura.

- El no. de funcions accessibles des d'un únic xip és alta.

El desavantatges de la lògica acoblada a emissor es comenten a continuació.

- Té un marge de soroll extremadament menor, és a dir, ±200 mV.

- La dissipació de potència és alta en comparació amb altres portes lògiques.

- Per connectar amb altres famílies lògiques, calen canvis de nivell.

- Fanout limita la càrrega capacitiva.

- En comparació amb TTL , les portes ECL són cares.

- En comparació amb CMOS i TTL, la immunitat al soroll ECL és pitjor.

Aplicacions

Les aplicacions de la lògica acoblada a emissor inclouen les següents.

- La lògica acoblada a l'emissor s'utilitza com a tecnologia de lògica i interfície en dispositius de comunicacions d'alta velocitat com les interfícies de transceptor de fibra òptica, xarxes Ethernet i ATM (mode de transferència asíncron).

- ECL és una família lògica basada en BJT on es pot aconseguir el seu funcionament d'alta velocitat utilitzant un canvi de tensió relativament petit i evitant que els transistors es moguin a la regió de saturació.

- ECL s'utilitza per fer els circuits ASLT dins de l'IBM 360/91.

- ECL evita la utilització de transistors apilats mitjançant l'ús d'un biaix i/p d'un sol extrem i retroalimentació positiva entre transistors primaris i secundaris per aconseguir una funció inversora.

- ECL s'utilitza en electrònica d'alta velocitat.

Així, això és una visió general d'una lògica acoblada d'emissors o ECL: circuit, funcionament, característiques, característiques i aplicacions. ECL és la família lògica més ràpida basada en BJT en comparació amb altres famílies lògiques digitals. Aconsegueix la seva màxima velocitat de funcionament mitjançant l'ús d'una petita variació de tensió i evitant que els transistors es moguin a la regió de saturació. Aquesta família lògica proporciona un retard de propagació d'1ns increïble i, a les últimes famílies ECL, aquest retard es redueix. Aquí teniu una pregunta per a vosaltres, quin és un nom alternatiu per a ECL?